Protocolos de comunicación - Niveles lógicos digitales

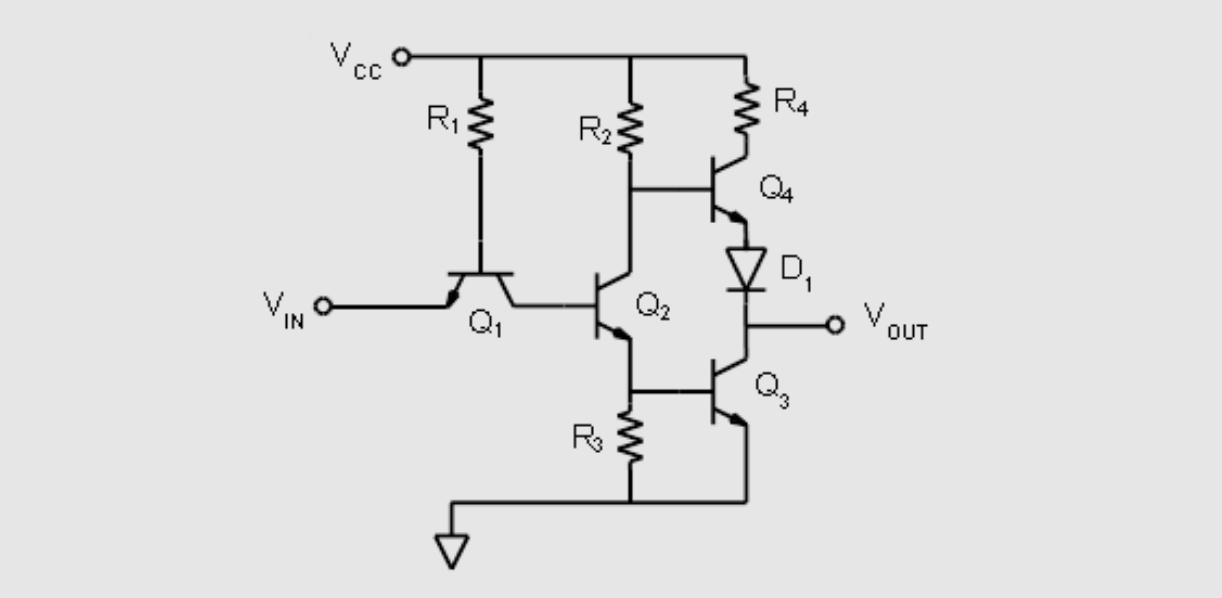

Interfaz de nivel TTL

TTL (Transistor-Transistor Logic) se basa en una estructura de transistores y su fuente de alimentación estándar es de 5V. Debido a que hay una gran diferencia entre 2.4V y 5V, las fluctuaciones de voltaje aumentan el consumo de energía del sistema, por lo que se ha desarrollado el nivel LVTTL (Low Voltage Transistor-Transistor Logic) que opera a 3.3V y 2.5V.

Características del nivel (LV) TTL:

- Los circuitos TTL son controlados por corriente, lo que les permite tener una alta velocidad y un corto tiempo de retardo de transmisión (5-10ns), pero consumen mucha energía.

- Los niveles TTL suelen tener una sobretensión considerable, por lo que se puede agregar una resistencia de 22Ω/33Ω en el extremo de inicio.

- Cuando un pin de nivel TTL está sin conexión, se considera internamente como un nivel alto. Si se requiere un nivel bajo, se debe conectar una resistencia de pull-down de menos de 1k.

- La velocidad de la interfaz de nivel TTL generalmente está limitada a 30MHz. Esto se debe a que la entrada del BJT tiene una capacidad de entrada de varios pF (formando un LPF). Si la señal de entrada supera cierta frecuencia, se perderá la señal.

- Su capacidad de conducción suele ser de varios decenas de mA. Las señales que funcionan normalmente tienen un voltaje relativamente alto. Si se acerca a un circuito ECL con un voltaje de señal más bajo, se producirán problemas de interferencia notable.

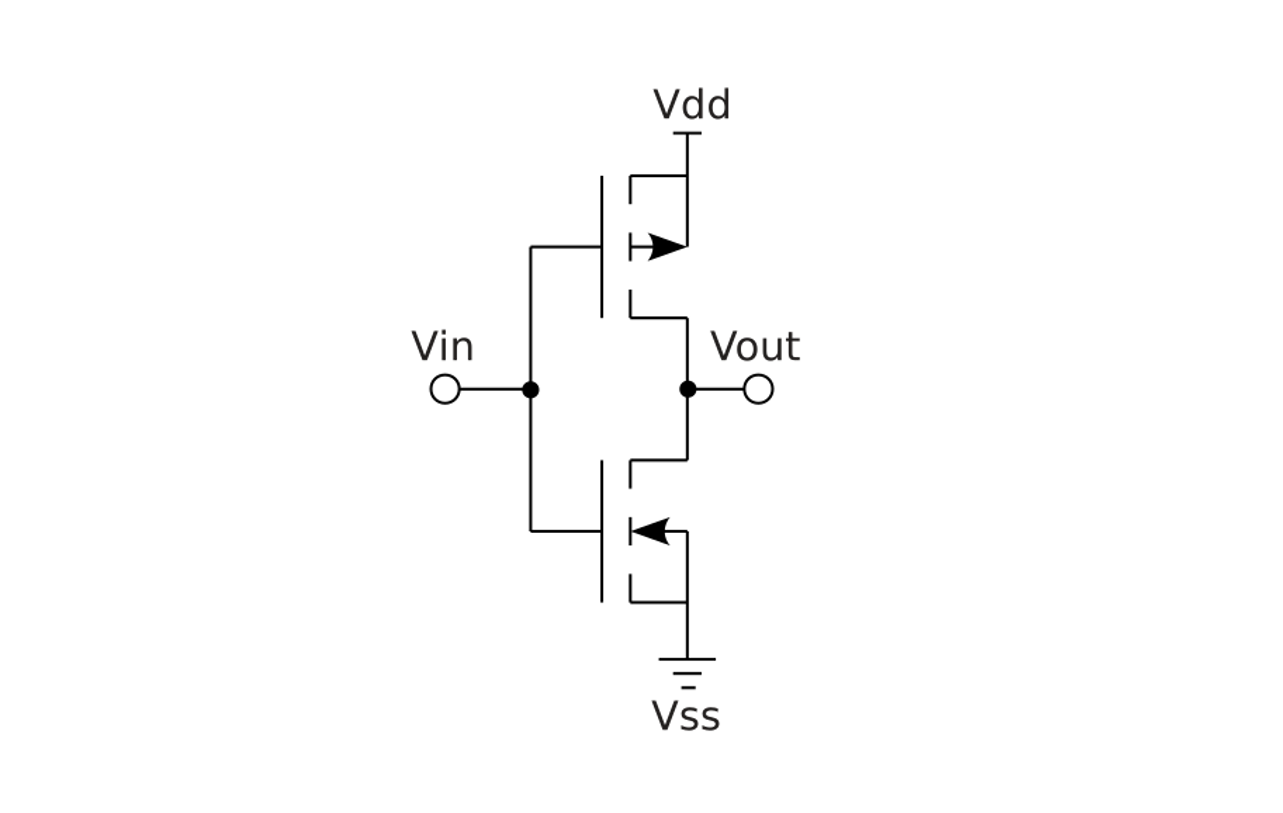

Interfaz de nivel CMOS

CMOS (Complementary Metal Oxide Semiconductor) se basa en una estructura compuesta por NMOS y PMOS, y su fuente de alimentación estándar es de 5V. Al igual que TTL, CMOS también ha derivado el estándar de nivel LVCMOS, y debido a que la tensión de conducción de los MOSFET es más baja que la de los transistores bipolares, LVCMOS puede utilizar voltajes más bajos para la comunicación. LVCMOS tiene los estándares de 3.3V, 2.5V, 1.8V, 1.5V y 1.2V.

Características del nivel (LV) CMOS:

- Los circuitos CMOS son controlados por voltaje, lo que les da una velocidad más lenta y un mayor tiempo de retardo de transmisión (25-50ns), pero consumen menos energía. Sin embargo, en frecuencias de conmutación altas, la serie CMOS en realidad consume más energía que TTL.

- La interfaz CMOS tiene una mayor tolerancia al ruido en comparación con la interfaz TTL, y su impedancia de entrada es mucho mayor que la de TTL. En condiciones normales, el consumo de energía y la capacidad de anti-interferencia de CMOS son superiores a los de TTL.

- La estructura CMOS tiene una estructura de silicio controlable en parásito, y cuando la entrada o el pin de entrada supera un cierto valor por encima de VCC (por ejemplo, 0.7V en algunos chips), si la corriente es lo suficientemente alta, puede causar el efecto de latch-up y provocar la destrucción del chip.

- La impedancia de entrada del circuito CMOS es muy alta, por lo que su capacidad de acoplamiento capacitivo puede ser muy pequeña y no se requieren capacitores electrolíticos grandes. Debido a que los circuitos CMOS suelen tener una capacidad de conducción más débil, es necesario convertirlos a TTL antes de conducir circuitos ECL. Además, al diseñar circuitos de interfaz CMOS, es importante evitar una carga capacitiva excesiva, ya que esto ralentizará el tiempo de subida y aumentará el consumo de energía del dispositivo (ya que la carga capacitiva no consume energía).

Comparación de los estándares de cada nivel

Los circuitos digitales tienen un estándar de doble umbral. Aunque solo se representan dos estados, 0 y 1, en los circuitos reales se acuerda mediante un estándar de doble umbral qué voltaje es considerado como 0 y qué voltaje es considerado como 1.

| \(VCC\) | \(V_{OH}\) | \(V_{IH}\) | \(V_{IL}\) | \(V_{OL}\) | \(GND\) | |

|---|---|---|---|---|---|---|

| 5V TTL | 5.0 | 2.4 | 2.0 | 0.8 | 0.4 | 0.0 |

| 3.3V LVTTL | 3.3 | 2.4 | 1.5 | 0.8 | 0.4 | 0.0 |

| 5V CMOS | 5.0 | 4.5(0.9*VCC) | 3.5(0.7*VCC) | 1.5(0.3*VCC) | 0.5(0.1*VCC) | 0.0 |

| 3.3V CMOS | 3.3 | 2.97(0.9*VCC) | 2.31(0.7*VCC) | 0.99(0.3*VCC) | 0.33(0.1*VCC) | 0.0 |

| 2.5V CMOS | 2.5 | 2.0 | 1.7 | 0.7 | 0.4 | 0.0 |

| 1.8V CMOS | 1.8 | 1.35 | 1.17 | 0.63 | 0.45 | 0.0 |

Comunicación en serie y en paralelo

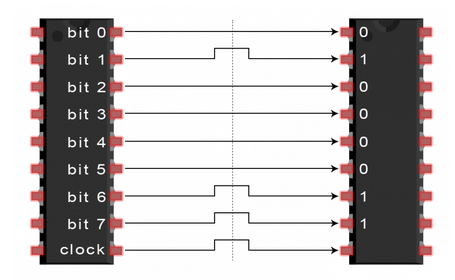

Los bits de datos se pueden transmitir en forma paralela o en serie. En la comunicación en paralelo, los bits de datos se envían simultáneamente, cada uno a través de una línea separada. La siguiente imagen muestra la transmisión en paralelo de la letra C en binario (01000011):

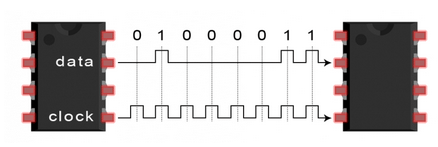

En la comunicación en serie, los bits se envían uno a uno a través de una sola línea. La siguiente imagen muestra la transmisión en serie de la letra C:

Referencias y agradecimientos

- "Analog Engineer’s Pocket Reference"

- Understanding the Working Principle, Advantages, Disadvantages, and Application Cases of the SPI Bus

- [FPGA13][Circuit] Interface Voltage Standards

Dirección original del artículo: https://wiki-power.com/

Este artículo está protegido por la licencia CC BY-NC-SA 4.0. Si desea reproducirlo, por favor indique la fuente.Este post está traducido usando ChatGPT, por favor feedback si hay alguna omisión.