Fundamentos de pruebas de semiconductores - Conceptos básicos

Con el aumento de la integración de chips, las pruebas manuales ya no pueden satisfacer las demandas, por lo que se requiere el uso de equipos de prueba automatizados (ATE, por sus siglas en inglés, Automated Test Equipment). Debido a que los chips actuales son cada vez más complejos, las pruebas de banco convencionales no pueden satisfacer las demandas. ATE puede detectar la integridad de las funciones de los circuitos integrados y es el último proceso en la fabricación de chips, asegurando la calidad del producto. Las pruebas de chips son una parte integral de la cadena de suministro de la industria de semiconductores. Los dispositivos sometidos a pruebas se dividen principalmente en varias categorías: memoria, circuitos digitales, circuitos analógicos y circuitos de señal mixta.

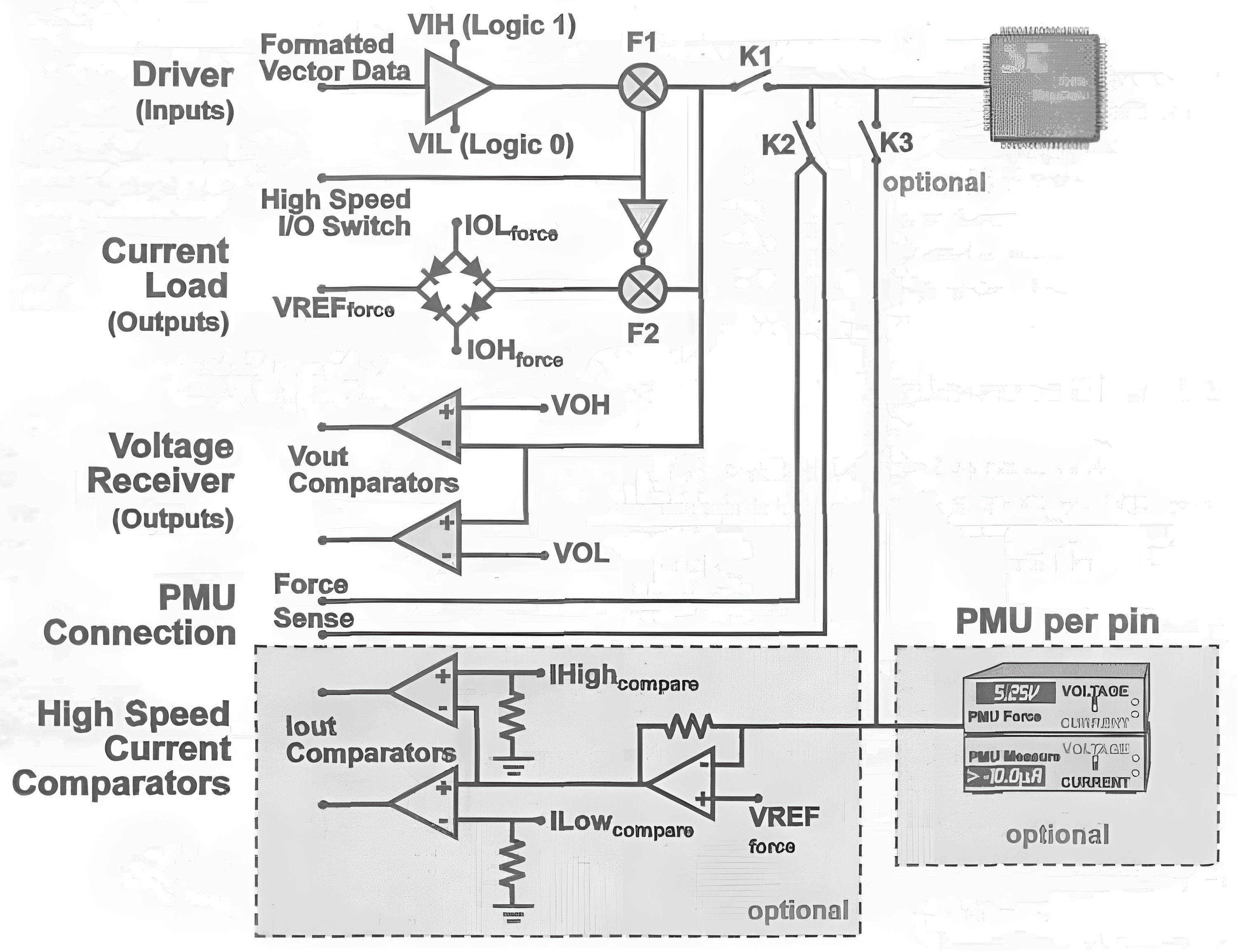

ATE tiene muchos subsistemas internos, que incluyen circuitos de accionamiento de alto y bajo nivel, cargas de corriente programables, comparadores para detectar voltajes de salida, circuitos de conexión PMU, comparadores de corriente de alta velocidad, interruptores de alta velocidad, entre otros.

Como se puede ver en el diagrama anterior, el sistema de prueba está compuesto principalmente por tres partes: entrada, salida y carga dinámica:

- Parte de entrada: proporciona voltajes VIL/VIH al DUT.

- Parte de salida: compara el voltaje de salida del DUT con VOL/VOH.

- Carga dinámica

- Genera un voltaje de salida mediante la carga de corriente IOL/IOH y lo compara con VOL/VOH.

- Compara directamente la corriente de salida con ILow/IHigh (generalmente solo en equipos de gama alta).

La prueba más básica consiste en medir los parámetros de corriente continua (DC) y corriente alterna (AC). Para los parámetros DC, se pueden utilizar métodos estáticos, como el uso de una tarjeta PE para la generación de señales y una PMU para medir la corriente o viceversa; también se pueden utilizar métodos funcionales, como la carga de corriente y el comparador de voltaje, y luego ejecutar un patrón de prueba.

Entrada y salida de señales

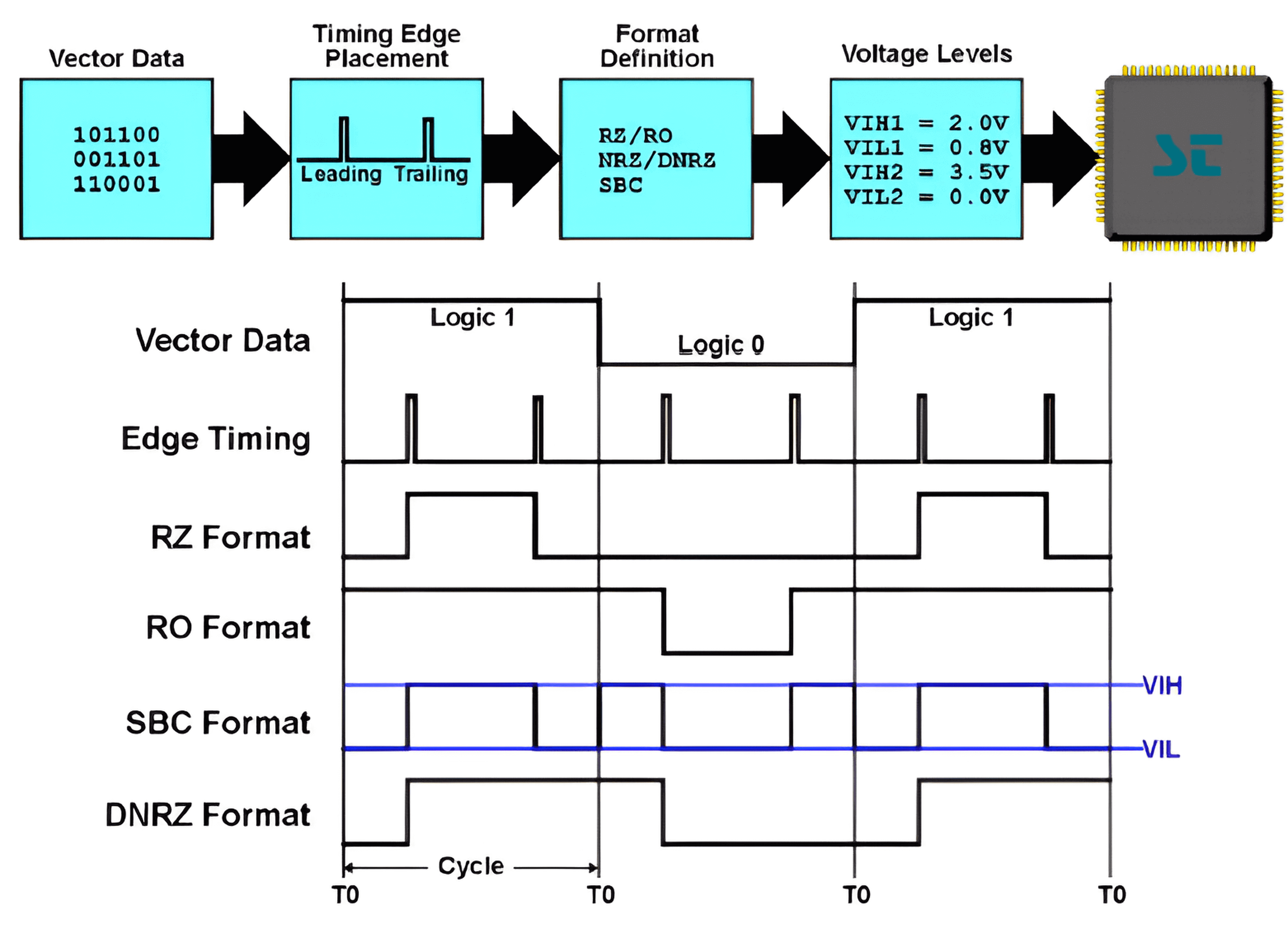

Cómo se generan e ingresan las señales al DUT:

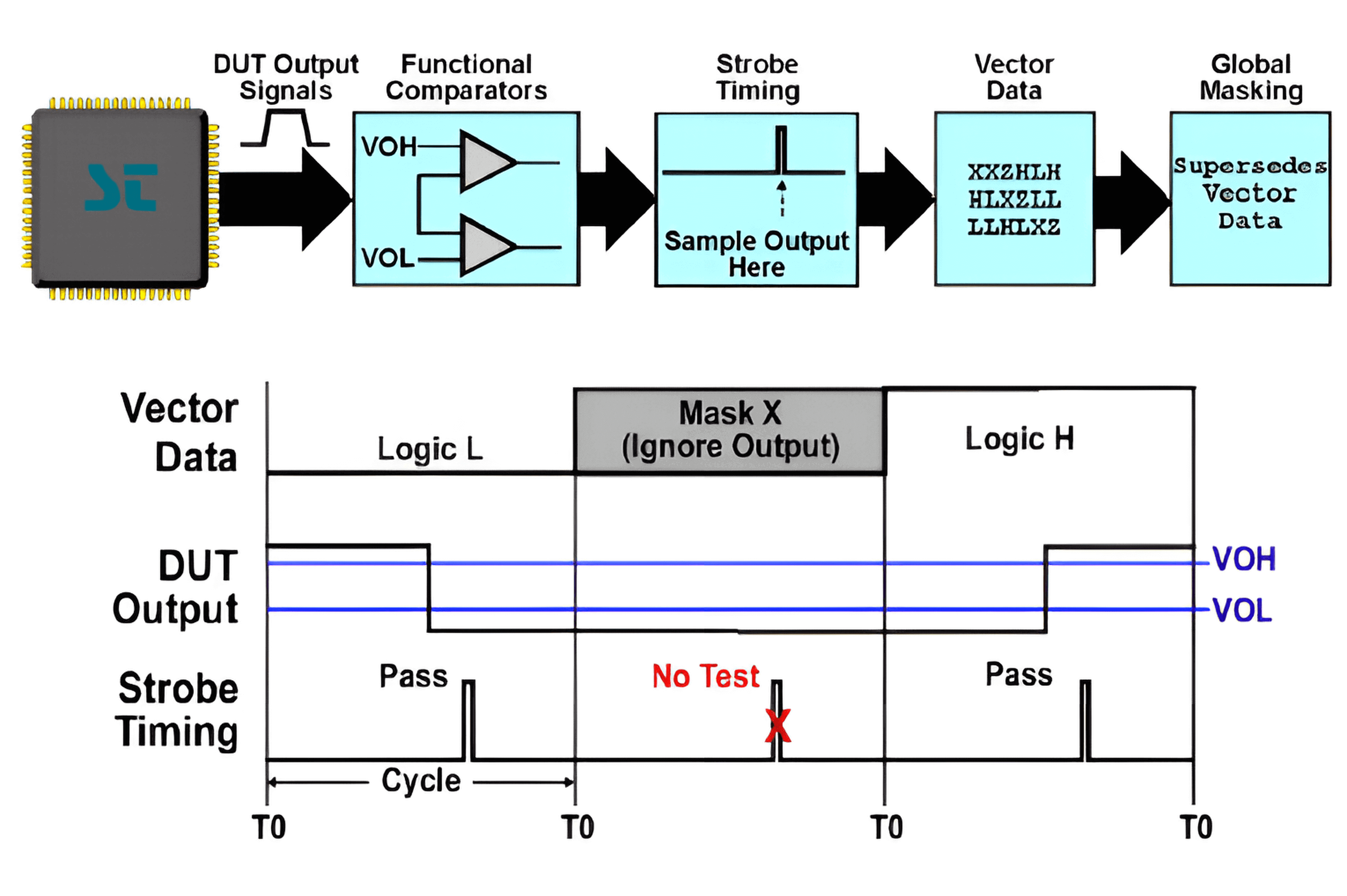

Cómo se leen y prueban las señales del DUT:

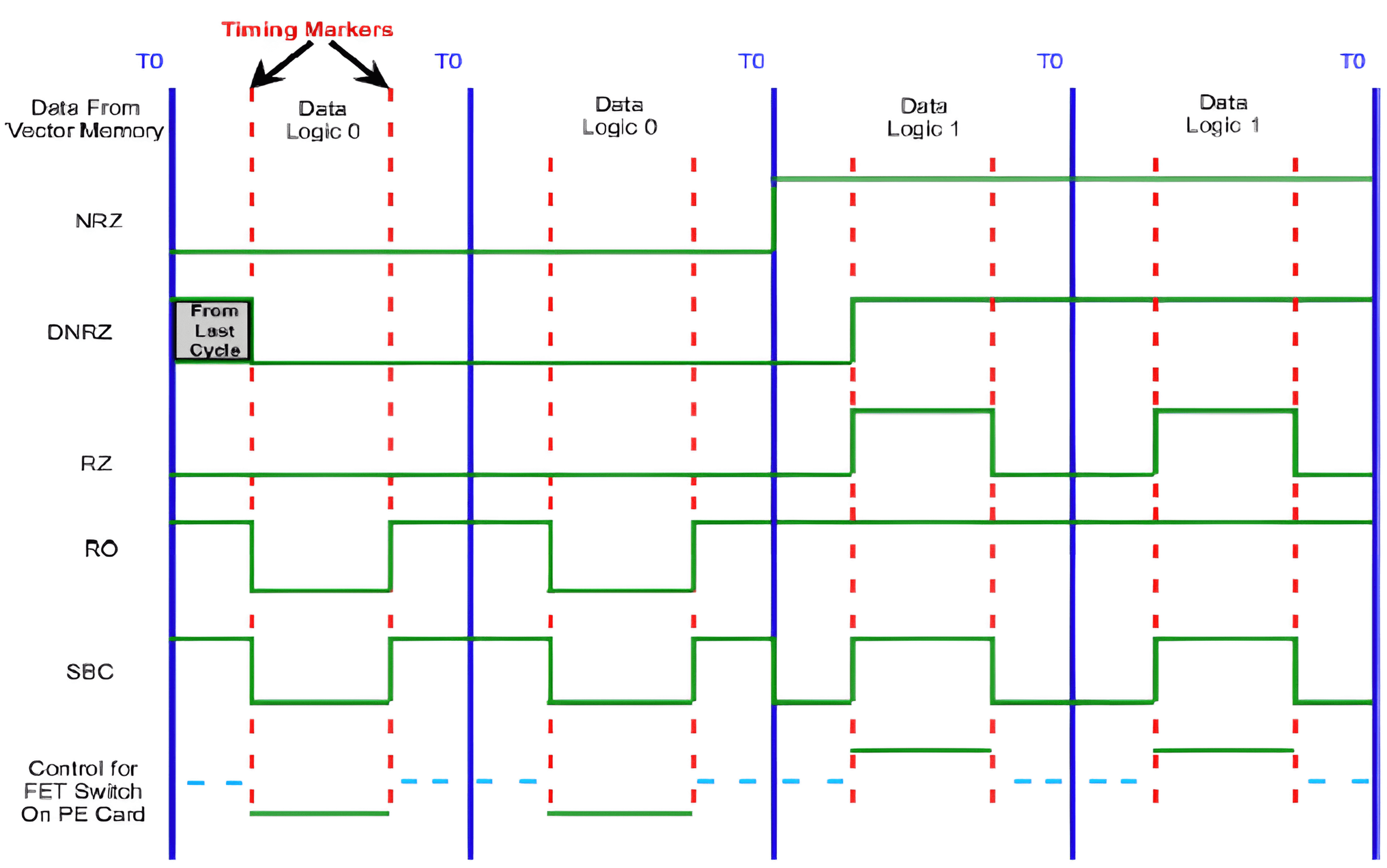

Formato de las señales de entrada

- RZ (Return to Zero): código de retorno a cero, transmite datos binarios dentro de un ciclo y, al finalizar el pulso de datos, debe mantenerse en bajo nivel. Este tipo de codificación puede transmitir simultáneamente la señal de reloj y los datos, pero debido a que parte del ancho de banda está ocupado por el retorno a cero, la eficiencia de transmisión es relativamente baja. La posición de las transiciones de subida y bajada puede ser controlada por el tiempo de flanco.

- RO (Return to One): código de retorno a uno, es opuesto al RZ y debe mantenerse en alto nivel. La posición de las transiciones de subida y bajada puede ser controlada por el tiempo de flanco.

- NRZ (Non Return to Zero): código no retorno a cero, a diferencia del RZ, no es necesario volver a cero, por lo que un ciclo completo se puede utilizar para transmitir datos, con una utilización del ancho de banda del 100%. Si se transmiten datos asíncronos de baja velocidad, no se requiere una línea de reloj, pero se debe acordar la velocidad de transmisión (como en UART); para la transmisión de datos síncronos de alta velocidad, se requiere una línea de reloj adicional. El NRZ no está controlado por el tiempo de flanco.

- DNRZ (Delayed Non Return to Zero): código no retorno a cero con retardo, es una forma de onda NRZ con un retardo de tiempo. El tiempo de retardo está controlado por el tiempo de flanco.

- SBC (Surrounded By Complement): complemento rodeado es una combinación de RZ y RO. Puede haber hasta 3 transiciones en cada ciclo, invirtiendo los datos en T0, mostrando un valor predefinido después de un cierto retardo y luego volviendo a invertir. SBC se utiliza principalmente para establecer/mantener el control de la señal.

- ZD (Impedance Drive): la unidad de control de impedancia se utiliza para abrir o cerrar (alta impedancia) los pines.

La señal de reloj generalmente se utiliza en formato RZ/RO, las señales con transiciones de subida válidas (como CS o READ) generalmente se utilizan en formato RZ; las señales con transiciones de bajada válidas (como OE) generalmente se utilizan en formato RO; las señales de datos que tienen requisitos de tiempo de establecimiento y retención generalmente se utilizan en formato SBC; otras señales de entrada pueden utilizar formatos NRZ o DNRZ.

Formato de las señales de salida

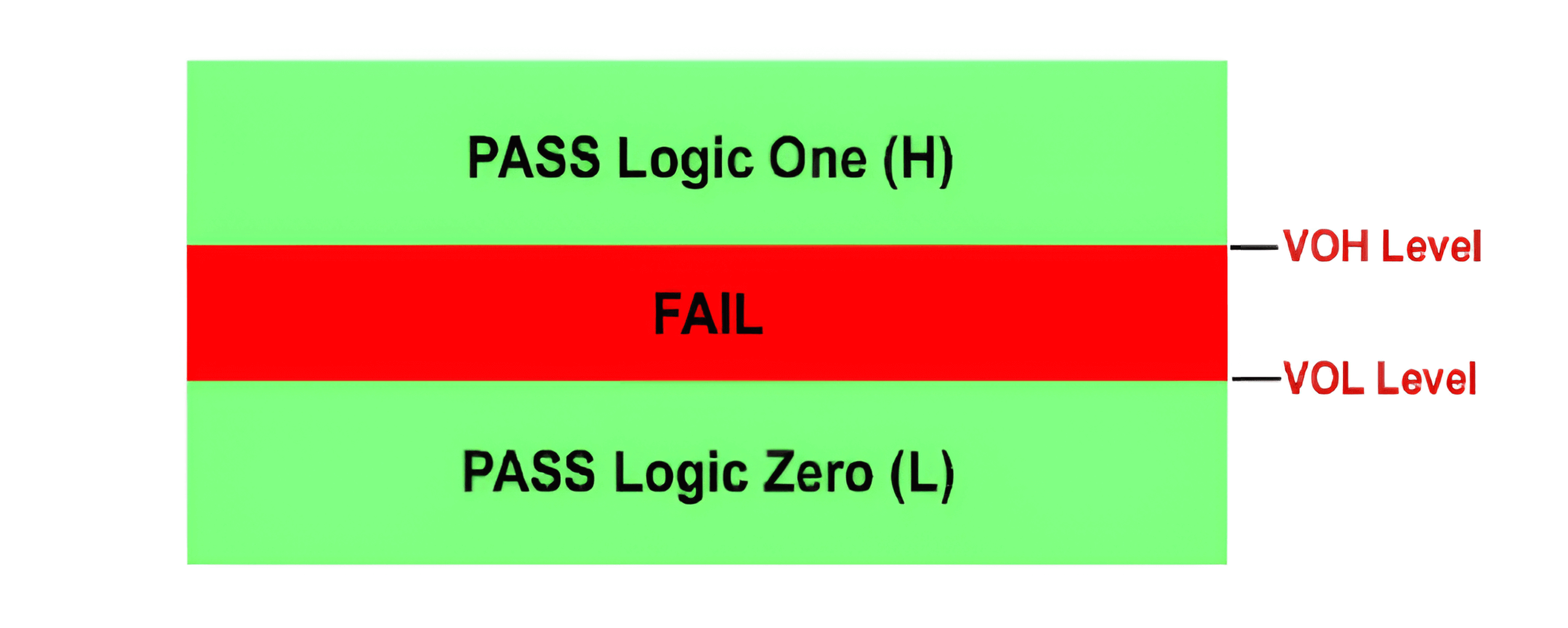

Salida de nivel alto y bajo

Cuando se trata de la lógica de niveles altos y bajos en las salidas de los pines, el nivel alto debe ser al menos más alto que VOH, y el nivel bajo debe ser al menos más bajo que VOL.

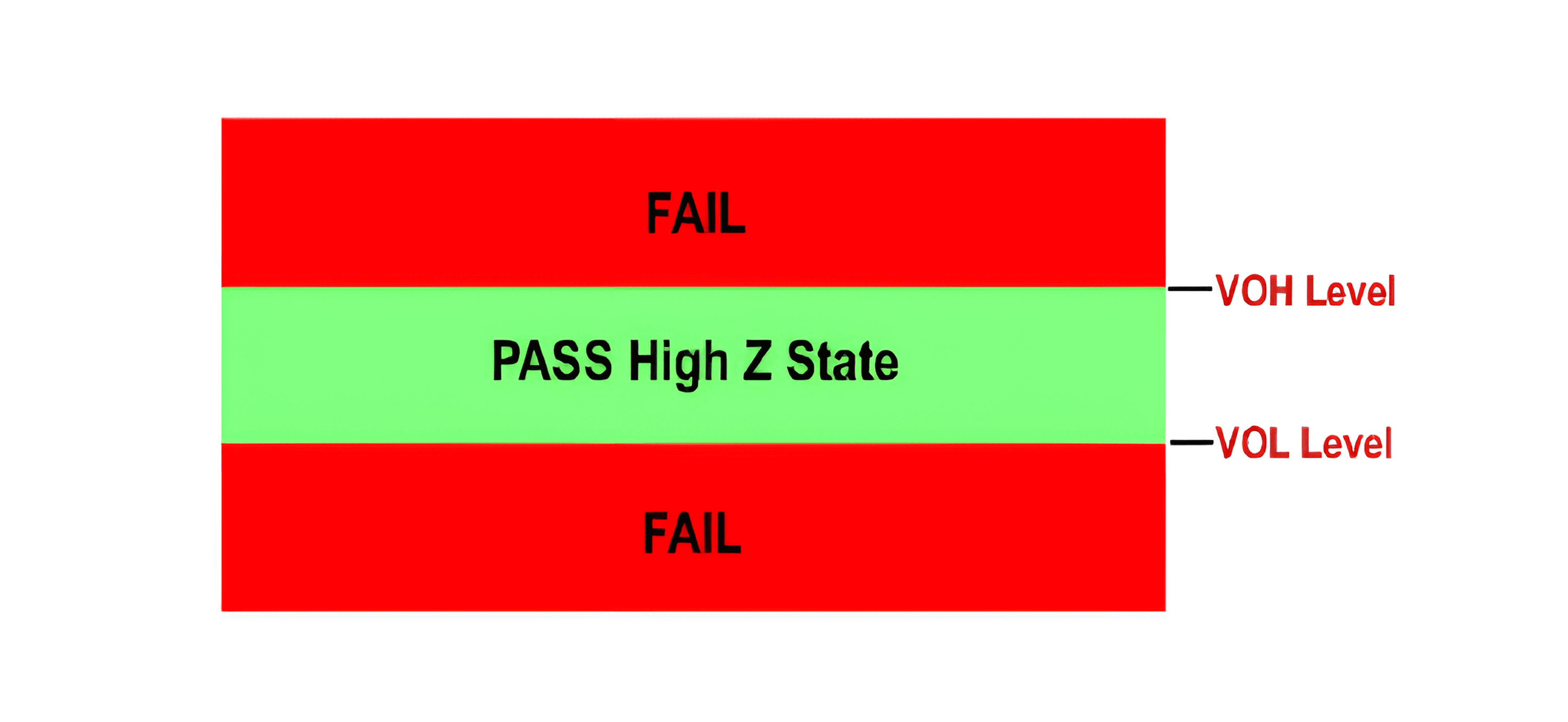

Salida en estado de alta impedancia

El pin del DUT es llevado a un voltaje entre VOL y VOH por una carga externa, por lo que no puede proporcionar voltaje ni corriente de salida.

Salida de corriente de carga

Algunos pines del DUT pueden proporcionar corriente de carga. Si el sistema de prueba tiene una carga de corriente programable, se puede realizar la prueba directamente. Si no, puede ser necesario agregar una resistencia externa para la prueba. La salida de corriente de carga debe cumplir con los valores especificados de IOL/IOH siempre que VOL/VOH estén dentro de los límites.

Explicación de términos comunes

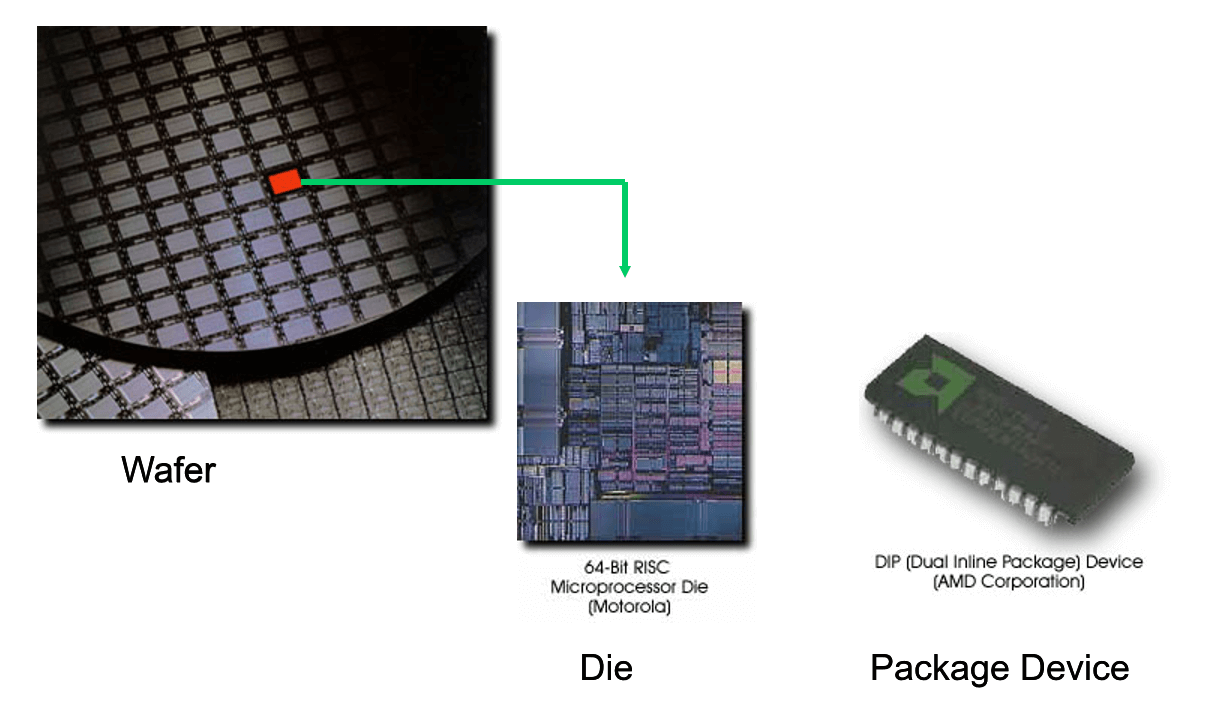

Oblea, dado y encapsulado

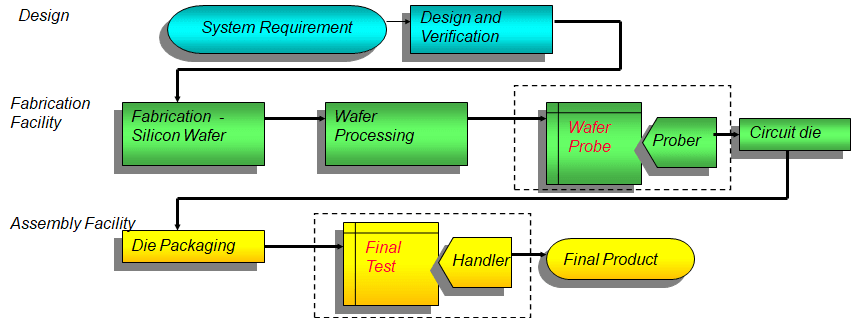

Proceso de diseño y fabricación de chips:

La relación entre la oblea (wafer), el dado (die, en plural dice, también conocido como chip desnudo) y el chip encapsulado (dispositivo empaquetado) es la siguiente:

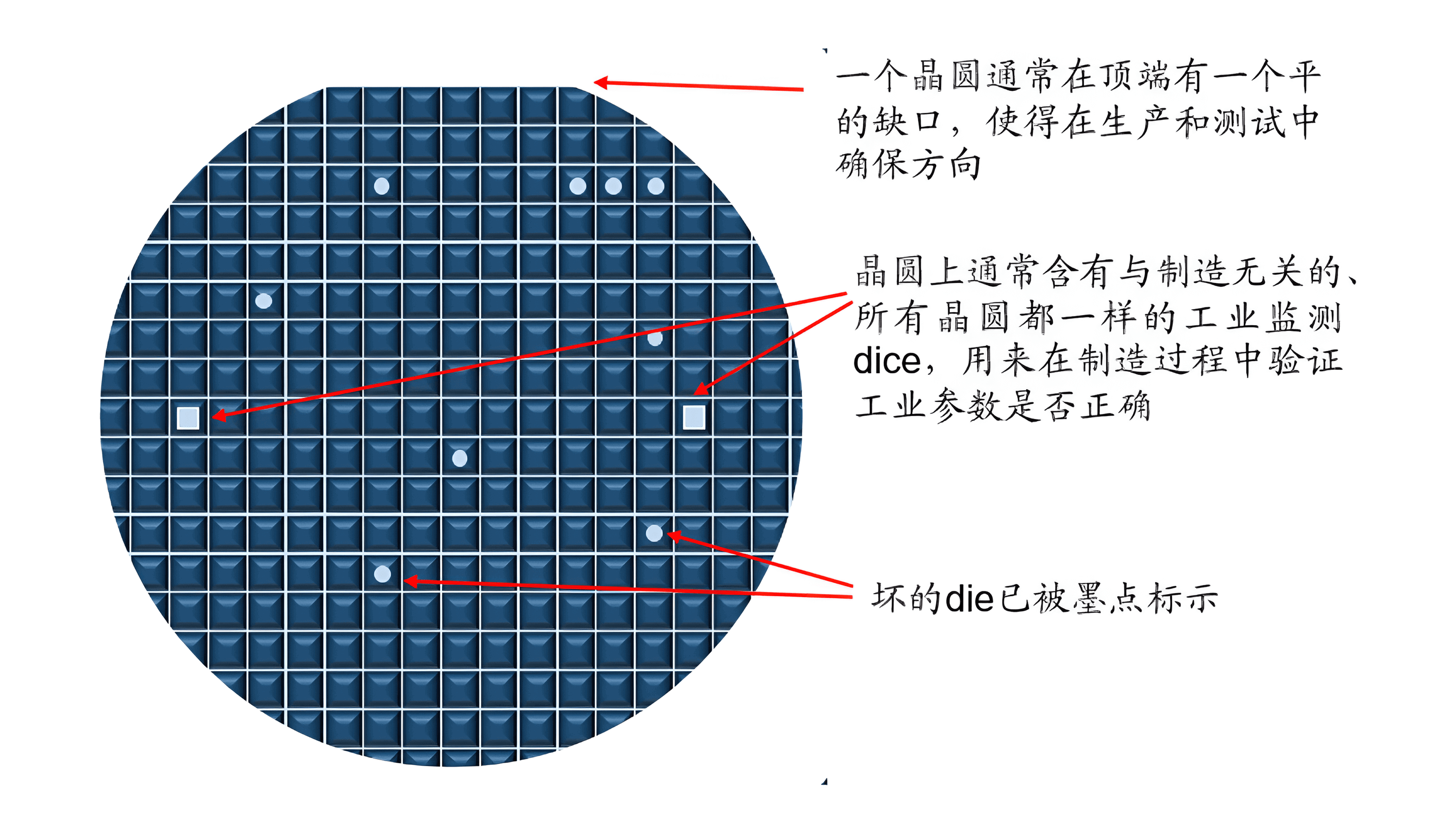

Oblea con pruebas y marcas de puntos:

Prueba CP y prueba FT

La prueba CP (Chip Probe) es una prueba de rendimiento y funcionalidad que se realiza en los pines del chip mientras aún está en la etapa de oblea, utilizando sondas para conectar los pines del chip. La prueba FT (Final Test) es la prueba final que se realiza después de que el chip ha sido encapsulado.

Términos de equipos de prueba

- DUT (Device Under Test): Dispositivo bajo prueba, se realiza la prueba del dispositivo a través de sus pines mediante señales externas. También conocido como UUT (Unit Under Test).

- DPS (Device Power Supplies): Dispositivos que suministran directamente voltaje y corriente al DUT.

- PMU (Precision Measurement Unit): Unidad de medición de precisión utilizada para medir las características de corriente continua del dispositivo de manera precisa.

- PPMU (Per Pin Measurement Unit): Unidad de medición por pin, con una PMU en cada pin para realizar mediciones.

- DIB (Device Interface Board): Placa de interfaz del dispositivo, también conocida como placa de carga.

- PIB (Probe Interface Board): Placa de interfaz de sonda utilizada para la prueba de obleas.

- PDP (Prober docking plate): Placa de acoplamiento de la sonda.

- PROBE CARD: Tarjeta con sondas utilizada para la prueba de obleas.

- BINNING: Proceso de clasificación del DUT según los resultados de la prueba.

- MANIPULATOR: Estructura que soporta la cabeza de prueba y permite su movimiento en múltiples direcciones.

- HANDLER: IC pick up and place handler, máquina de clasificación automática que coloca el DUT en el zócalo de la cabeza de prueba.

- PROBER: Plataforma de prueba que mueve la oblea debajo de las sondas de prueba.

Parámetros en la prueba

- VCC: Suministro de energía para dispositivos TTL.

- VDD: Suministro de energía para dispositivos CMOS.

- ICC: Corriente de accionamiento para dispositivos TTL.

- IDD: Corriente de accionamiento para dispositivos CMOS.

- VSS: Ruta de retorno de la fuente de alimentación.

- GND: Nivel de referencia, a menudo equivalente a VSS en dispositivos alimentados por una sola fuente de energía.

- IDD: Corriente consumida por dispositivos CMOS.

- ICC: Corriente consumida por dispositivos TTL.

- VIH: Límite de voltaje mínimo para una entrada de nivel alto (no se reconocerá como 0).

- VIL: Límite de voltaje máximo para una entrada de nivel bajo (no se reconocerá como 1).

- VOH: Límite de voltaje mínimo para una salida de nivel alto (no se reconocerá como 0).

- VOL: Límite de voltaje máximo para una salida de nivel bajo (no se reconocerá como 1).

- IIH: Corriente de entrada máxima permitida cuando el pin de entrada está en nivel alto.

- IIL: Corriente de fuga máxima permitida cuando el pin de entrada está en nivel bajo.

- IOH: Corriente de accionamiento/tirado (source) cuando la salida está en nivel alto.

- IOL: Corriente de fuga (sink) cuando la salida está en nivel bajo.

- IOZH: Corriente máxima permitida cuando la salida está en estado de alta impedancia y en nivel alto.

- IOZL: Corriente máxima permitida cuando la salida está en estado de alta impedancia y en nivel bajo.

- Retardo de propagación: Intervalo de tiempo desde la entrada de una señal hasta que la salida cambia.

- Tiempo de subida: Tiempo necesario para que una señal pase del 10% al 90% del nivel alto.

- Tiempo de caída: Lo contrario al anterior.

Hot Switching (Conmutación en caliente)

Hot Switching, también conocido como conmutación con corriente, se refiere a la acción de cambiar un relé mientras la corriente está fluyendo (puede haber voltaje, siempre y cuando ambos lados tengan el mismo voltaje). Esto puede acortar la vida útil del relé o dañarlo, por lo que es necesario evitar esta situación mediante programación.

Latch-up (Bloqueo)

Cuando se aplica un voltaje excesivo a un pin, se produce una corriente elevada en el dispositivo CMOS, lo que puede dañar o incluso destruir parte del circuito.

Stuck-At Fault (Fallo de estado fijo)

Stuck-At Fault (SAF) se refiere a un pin de señal que, debido a un defecto de fabricación, queda atrapado en un estado de nivel 0/1/Z, lo que provoca un fallo.

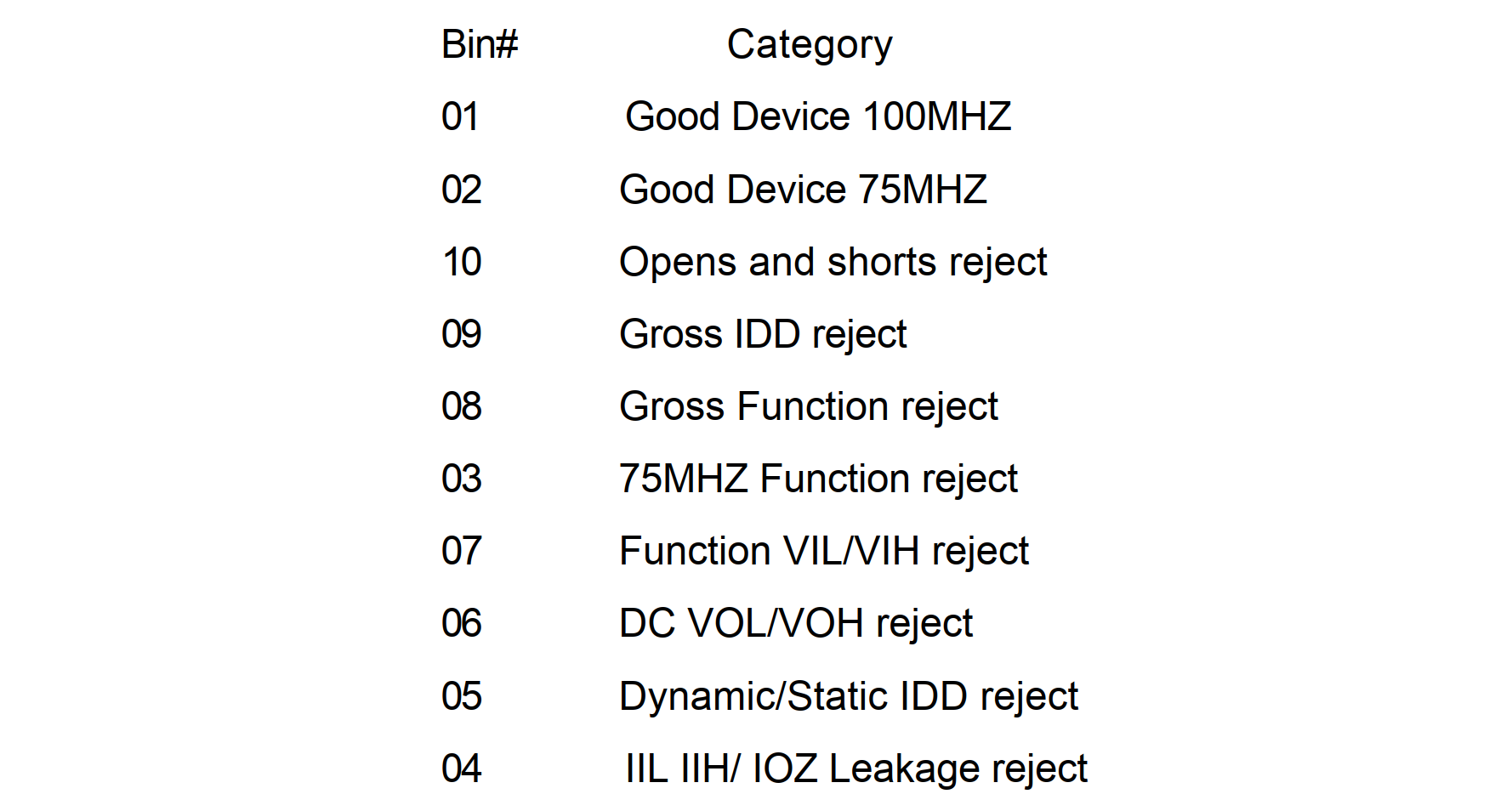

Binning

Binning es el proceso de clasificar y agrupar los Dispositivos Bajo Prueba (DUT) según los resultados de las pruebas. Por ejemplo:

El Hard Binning implica clasificar físicamente los DUT en dos grupos utilizando un manipulador u otro tipo de máquina. El Soft Binning implica registrar los productos defectuosos en el software sin clasificarlos físicamente.

El proceso de Binning requiere al menos dos grupos para distinguir si un resultado de prueba pasa o no.

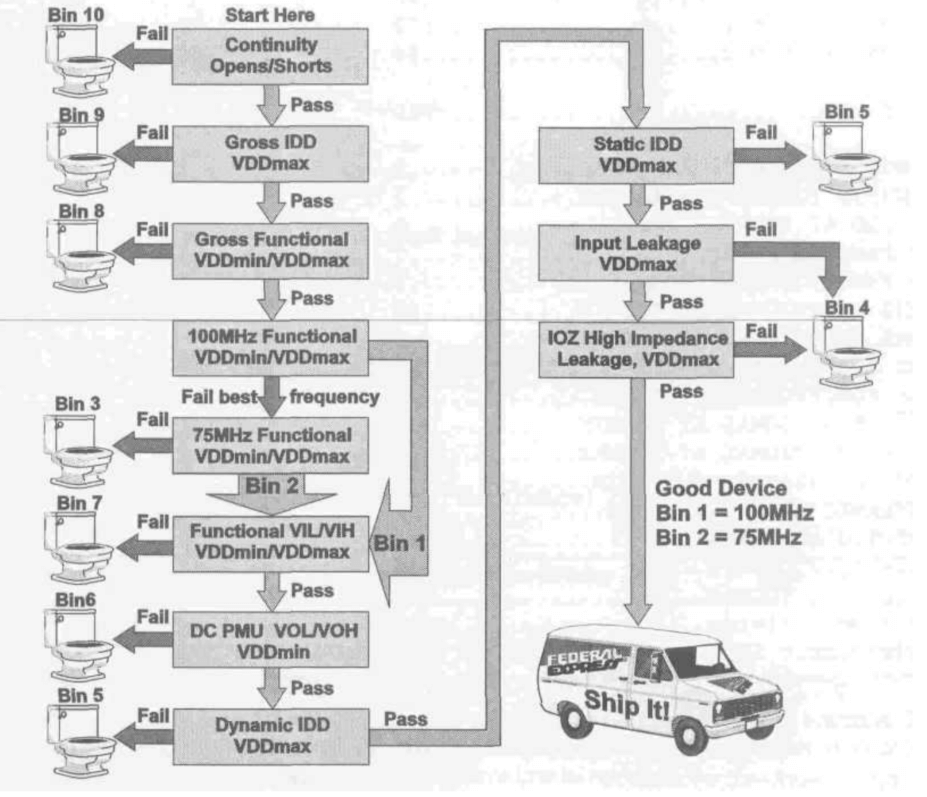

Program Flow (Flujo del programa)

El diseño del flujo del programa es crucial para todo el proceso de prueba. Por ejemplo, algunas pruebas de corriente continua (DC) requieren un preprocesamiento (configuración de la lógica del dispositivo, como pruebas de funcionalidad). Si se omite el preprocesamiento, los resultados de los pasos siguientes carecerán de sentido.

El diseño del flujo del programa debe tener en cuenta muchos factores, como el tamaño de la prueba, qué parámetros se deben probar y cómo se realizará el Binning. Normalmente, se utiliza un diagrama de flujo para asegurarse de que el flujo del programa cumpla con los requisitos.

Proyectos de prueba básicos:

- Prueba de Contacto/Continuidad: Verifica problemas de circuito abierto o cortocircuito en los pines del dispositivo.

- Prueba de Parámetros en Corriente Continua (DC PARAMETRICS TEST): Valida los parámetros de corriente y voltaje en corriente continua del equipo, incluyendo IDD.

- Prueba de Funcionalidad Digital (DIGITAL FUNCTIONAL TEST): Evalúa la funcionalidad lógica del DUT.

- Prueba de Temporización en Corriente Alterna (AC TIMING TEST): Verifica las especificaciones en corriente alterna, incluyendo la calidad de la señal de salida y los parámetros de temporización de la señal.

- Prueba de Señal Mixta (MIXED SIGNAL TEST): Valida la lógica de los circuitos analógicos y digitales del DUT.

- Otros tipos de pruebas incluyen dispositivos de RF (RF Devices), dispositivos automotrices (Automotive Devices), dispositivos de memoria (Memory Devices), dispositivos de gestión de energía (Power Management Devices), dispositivos RFID y dispositivos digitales de alta velocidad (High Speed Digital devices).

Referencias y Agradecimientos

- "The Fundamentals Of Digital Semiconductor Testing"

- 半导体设备系列研究三 - 半导体检测设备:芯与屏相融,光与电交汇

- 闩锁效应(Latch-up)详解

- https://www.eefocus.com/ansonguo/blog?p=1

Dirección original del artículo: https://wiki-power.com/

Este artículo está protegido por la licencia CC BY-NC-SA 4.0. Si desea reproducirlo, por favor indique la fuente.Este post está traducido usando ChatGPT, por favor feedback si hay alguna omisión.