Integridad de la señal - Distorsión 🚧

Los problemas de distorsión de la señal en una red única se dividen en tres aspectos: reflexión, problemas de calidad de la señal y errores de sincronización.

Reflexión

La causa fundamental de la reflexión es un cambio en la impedancia instantánea en la dirección de avance de la señal. Las posibles fuentes de cambio de impedancia incluyen: el extremo del cable de interconexión, cambios en el área de la sección transversal del cable, cambios de capa, brechas en el plano de retorno, componentes adicionales como conectores, y la topología de la disposición de los cables.

Fuentes de reflexión

Reflexión en puntos de cambio de impedancia

Cuando hay un cambio abrupto en la impedancia de la línea de transmisión, parte de la señal se reflejará en la dirección opuesta y otra parte continuará transmitiéndose, pero con una amplitud modificada. El valor de la señal reflejada depende de la cantidad de cambio en la impedancia instantánea. Si asumimos que la impedancia instantánea en la primera región es \(Z_1\) y en la segunda región es \(Z_2\), entonces el coeficiente de reflexión, que es la relación entre la amplitud de la señal reflejada y la amplitud de la señal incidente, se calcula de la siguiente manera:

Se puede observar que cuanto mayor sea la diferencia de impedancia entre las dos regiones, mayor será la cantidad de señal reflejada. Por ejemplo, si una señal de 1V se propaga a lo largo de una línea de transmisión con una impedancia característica de 50Ω y entra en una región con una impedancia característica de 75Ω, el coeficiente de reflexión se calcula como 20%, lo que significa que la tensión reflejada será de 0.2V.

Reflexión en cargas resistivas

La terminación de la línea de transmisión puede tener tres casos especiales: circuito abierto, cortocircuito y coincidencia de impedancia. Supongamos que la impedancia característica de la línea de transmisión es de 50Ω y la tensión incidente es de 1V, y analicemos cada caso:

- En el caso de un circuito abierto, la impedancia en el extremo es infinita y el coeficiente de reflexión tiende a 1, lo que significa que toda la señal incidente se reflejará en la dirección de la fuente. La suma de las tensiones incidente y reflejada en el punto de circuito abierto será de 2V.

- En el caso de un cortocircuito (es decir, cuando la impedancia en el extremo es 0), el coeficiente de reflexión será -1. Cuando la señal incidente llegue al extremo lejano, se generará una señal reflejada de -1V, que se propagará hacia la fuente. Por lo tanto, la tensión en este punto será de 0V.

- En el caso de una coincidencia de impedancia (es decir, cuando la impedancia en el extremo coincide con la impedancia característica de la línea de transmisión, que es de 50Ω), el coeficiente de reflexión será 0, lo que significa que no habrá tensión reflejada. La tensión en el extremo será únicamente la señal incidente.

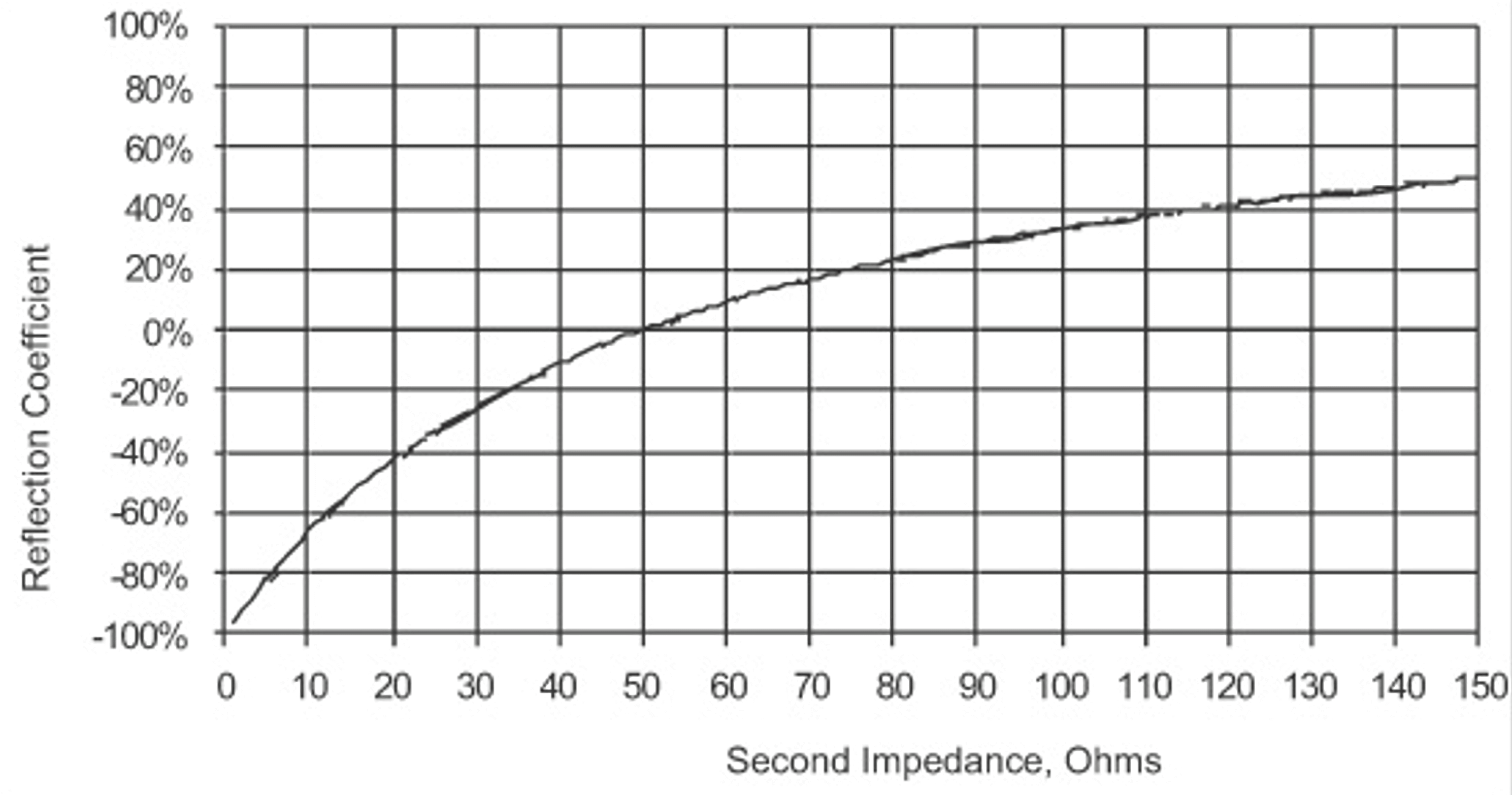

En general (con una impedancia de 50Ω), la relación entre la impedancia en la región 2 y el coeficiente de reflexión se muestra en el siguiente gráfico:

Cuando la impedancia en la región 2 es menor que la impedancia en la región 1, el coeficiente de reflexión será negativo y la tensión reflejada será negativa. Por ejemplo, si la carga resistiva en el extremo es de 25Ω, el coeficiente de reflexión será -0.33, lo que significa que se reflejará una tensión de -0.33V hacia la fuente, y la tensión real en el extremo será de 1+(-0.33)=0.67V.

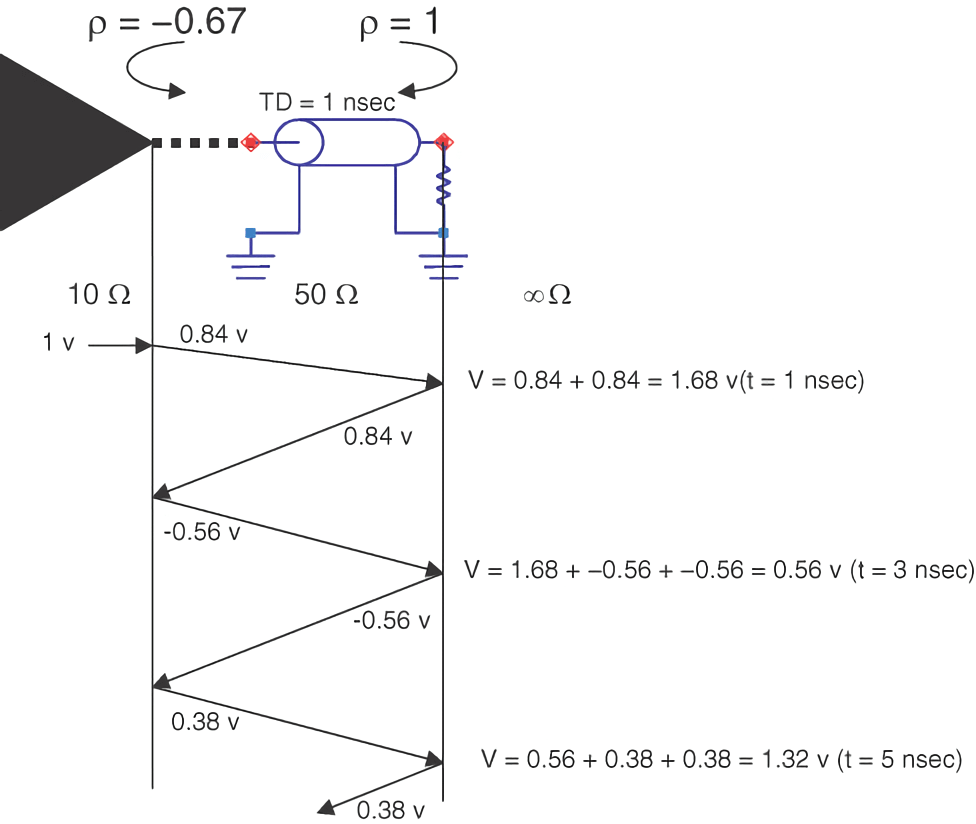

Diagrama de rebote

Si conocemos el retardo de la línea de transmisión, las impedancias en cada región por las que pasa la señal y el voltaje inicial del controlador, podemos calcular el voltaje en cada superficie de reflexión o en cualquier momento dado.

Supongamos que el voltaje de la fuente del controlador es de 1V, con una resistencia interna de 10Ω, y que el extremo de la línea de transmisión es un circuito abierto. Podemos calcular el siguiente diagrama y curva de rebote utilizando la fórmula de reflexión:

Formas de manifestación de la reflexión

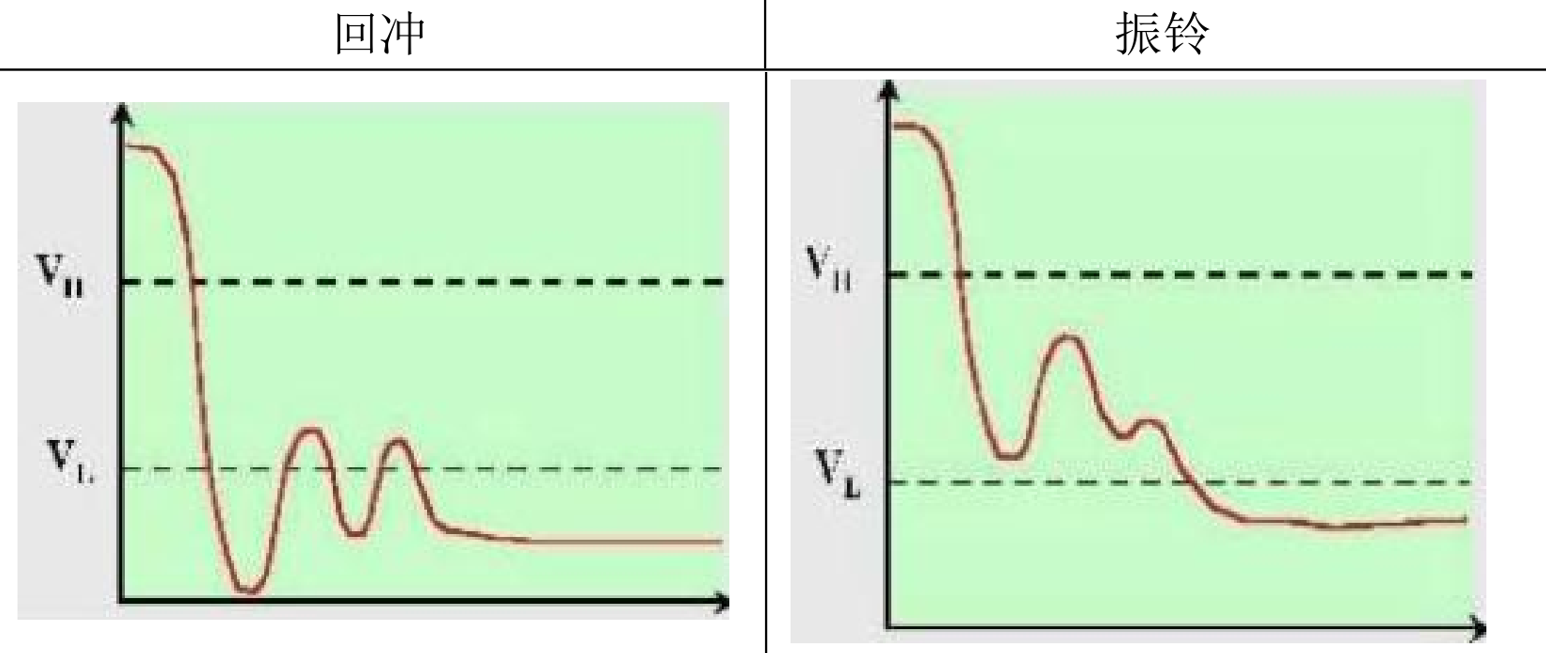

La reflexión generalmente se manifiesta como sobrepico, subpico y oscilación.

Sobrepico

El sobrepico se refiere al primer pico de oscilación, que puede ser positivo o negativo. El riesgo es que pueda dañar los dispositivos (superando el voltaje de alimentación o cayendo por debajo del voltaje de tierra). Además, el sobrepico puede convertirse en una fuente de interferencia y causar crosstalk en otros dispositivos. El subpico puede hacer que el voltaje negativo en los pines polarice directamente el sustrato PN (diodo parásito), lo que puede provocar una corriente alta y una apertura del circuito.

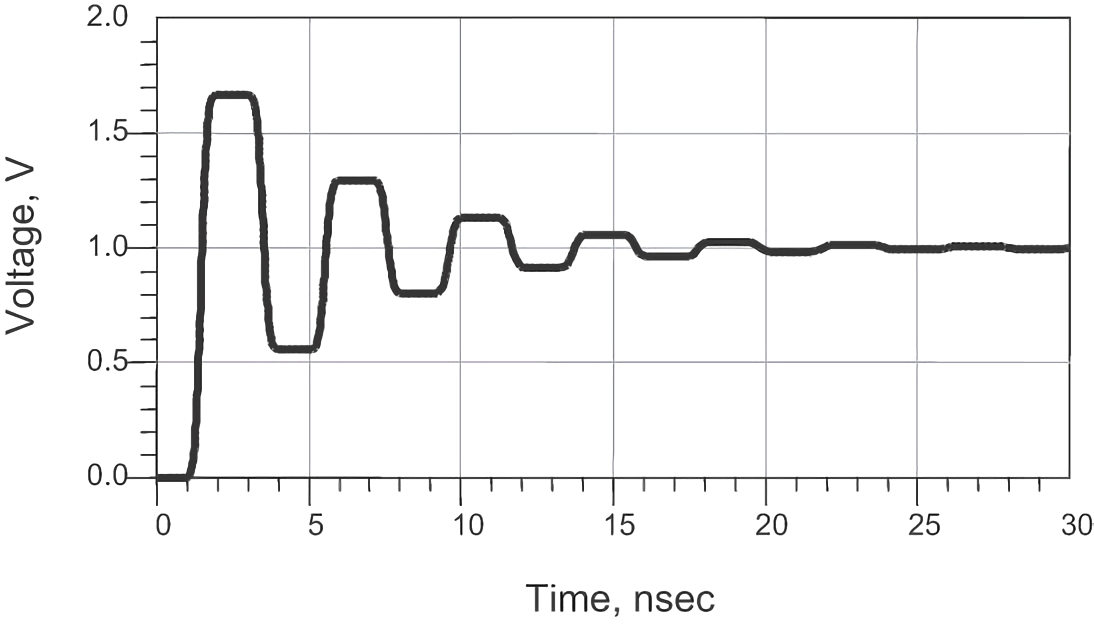

Oscilación (rebote)

El rebote se refiere a múltiples cruces de los niveles de voltaje críticos, mientras que la oscilación implica múltiples ciclos antes de que el voltaje regrese a su nivel normal.

El riesgo del rebote es similar al del sobrepico múltiple, ya que se encuentra en un estado incierto entre los niveles alto y bajo. La causa de esto es una mala coincidencia de impedancias (demasiado alta o demasiado baja).

Métodos para solucionar la reflexión

La solución a la reflexión consiste en mantener la impedancia de los cables de interconexión lo más constante posible. A continuación, se presentan algunas medidas específicas:

- Use interconnects with controllable impedance.

- Increase resistance matching, the recommended practice is to use series resistors at the beginning or parallel resistors at the end.

- Follow wiring rules that maintain a constant impedance along the line topology and minimize branch length.

- Fine-tune the geometric characteristics of the lines, such as avoiding right angles or sharp angles.

- Route the PCB traces away from sources of interference and coupling paths.

Timing Errors

The time delay difference between two or more signal paths is called skew. When there is unexpected skew between signal lines and clock lines, it can lead to false triggering and logic errors. When there is skew between differential lines, some differential signals may become common-mode signals, causing distortion.

References and Acknowledgments

- "Signal Integrity and Power Integrity Analysis"

- "Signal Integrity Revealed - Dr. Yu's SI Design Notes"

- What Every PCB Designer Should Know - Crosstalk Explained (with Eric Bogatin)

- "Hardware Signal Quality SI Test Specification"

- Analysis of Crosstalk in Transmission Lines

Dirección original del artículo: https://wiki-power.com/

Este artículo está protegido por la licencia CC BY-NC-SA 4.0. Si desea reproducirlo, por favor indique la fuente.

Unfinished draft 🚧:

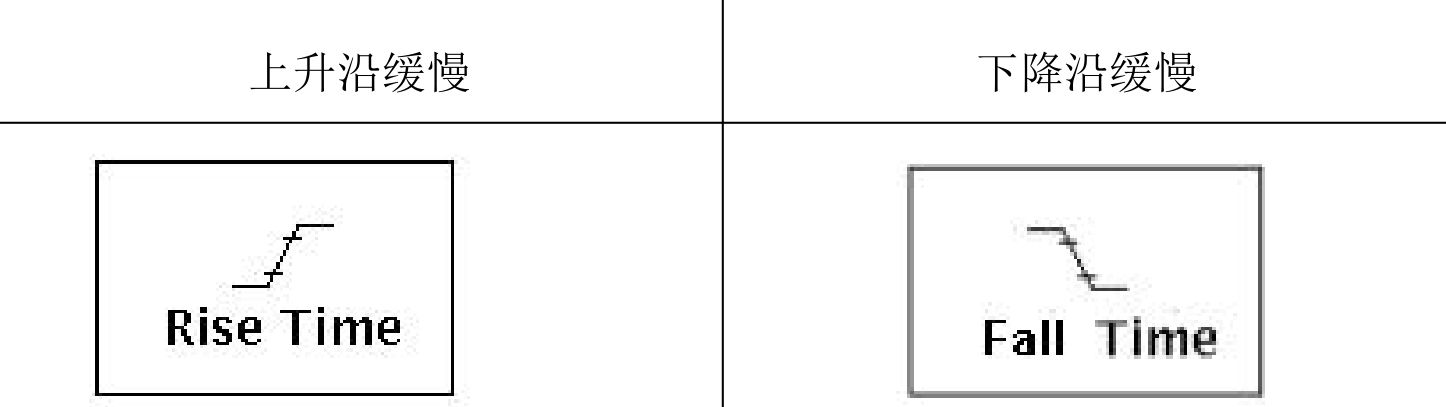

The slow generation of signal edges can also be caused by insufficient driving capability or excessive load (e.g., too high link impedance).

The methods to solve the slow generation of signal edges are:

- Increase the driving capability.

- Reduce the load.

Due to insufficient driving or excessive load, the slow generation of signal edges is often accompanied by a low signal amplitude.

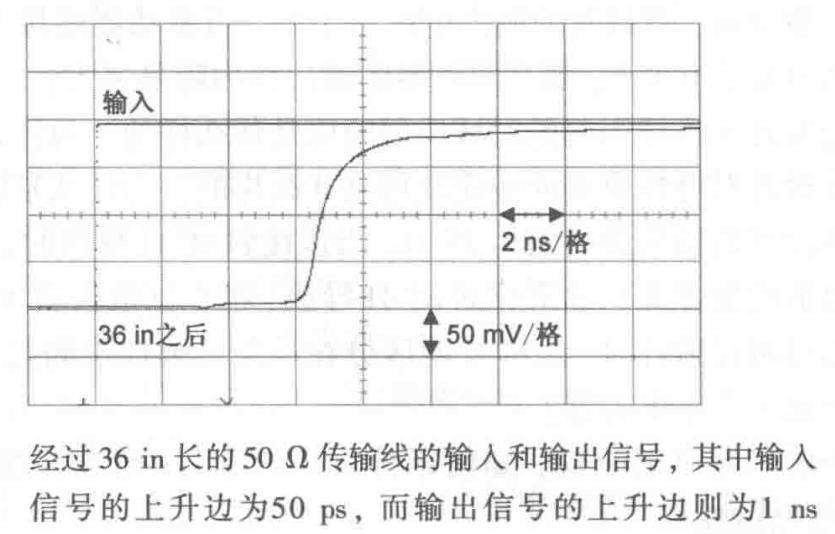

Rise Edge Degradation

Adverse Effects of Lossy Lines

When a signal with fast-changing edges passes through a section of actual transmission line, the rise edge will be elongated:

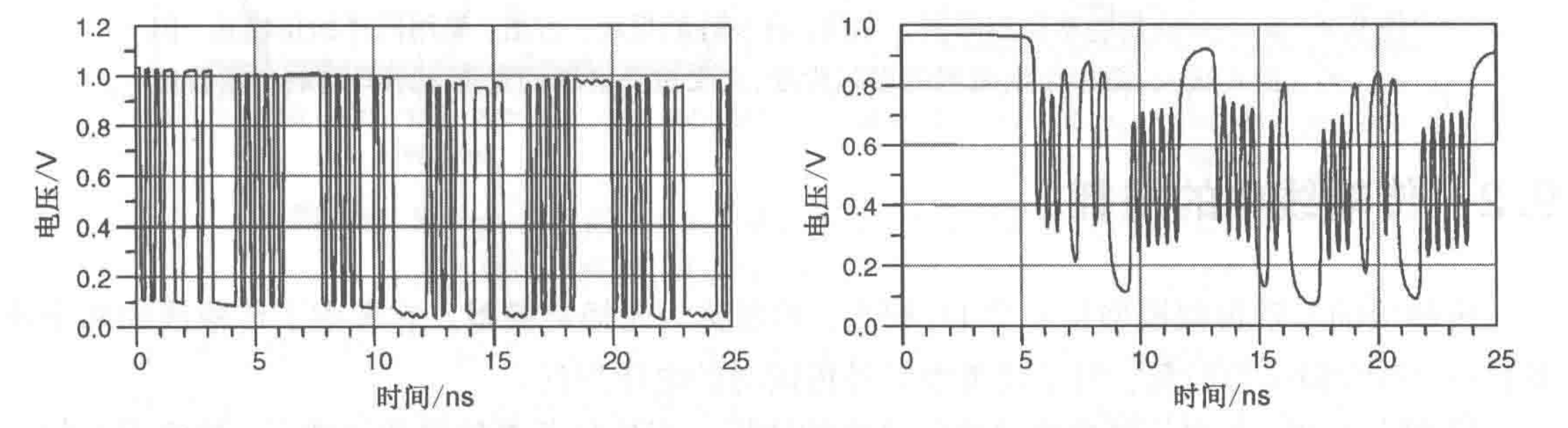

The signal quality issues caused by rise edge degradation are due to frequency-dependent losses in the wire/dielectric. These losses are greater at high frequencies than at low frequencies, resulting in slow signal edges. When the rise edge degrades to near the unit interval of the signal, 1 bit of information will leak into the next or even several bits, causing data sampling errors. This effect is called intersymbol interference (ISI) and is the main cause of problems when the data rate is greater than or equal to 1Gbps.

If the rise edge degradation causes the rise edge to elongate close to the unit interval, intersymbol interference may occur:

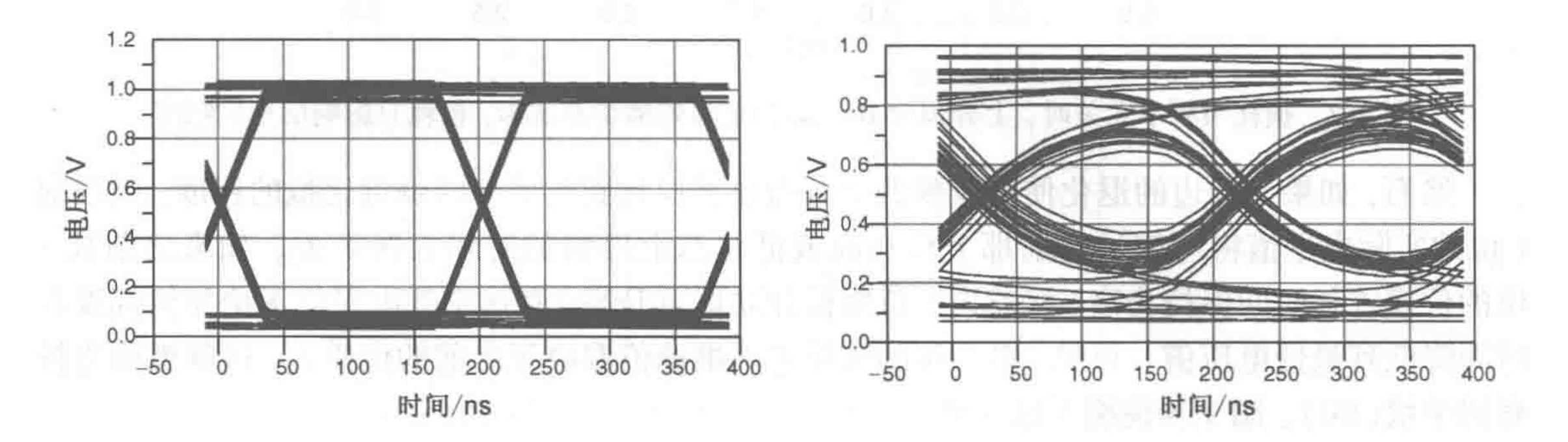

The quality assessment of high-speed signals can be done using an eye diagram, which can measure the bit error rate (the left diagram shows a slight loss, while the right diagram shows a larger loss):

Losses in Transmission Lines

When a signal propagates along a transmission line, there are five ways in which energy is lost at the receiving end:

- Radiation loss

- Coupling to adjacent traces

- Impedance mismatch

- Wire loss

- Dielectric loss

Wire Loss (Wire Resistance and Skin Effect)

Este post está traducido usando ChatGPT, por favor feedback si hay alguna omisión.