Communication Protocol - Ethernet 🚧

References and Acknowledgements

Original: https://wiki-power.com/ This post is protected by CC BY-NC-SA 4.0 agreement, should be reproduced with attribution.

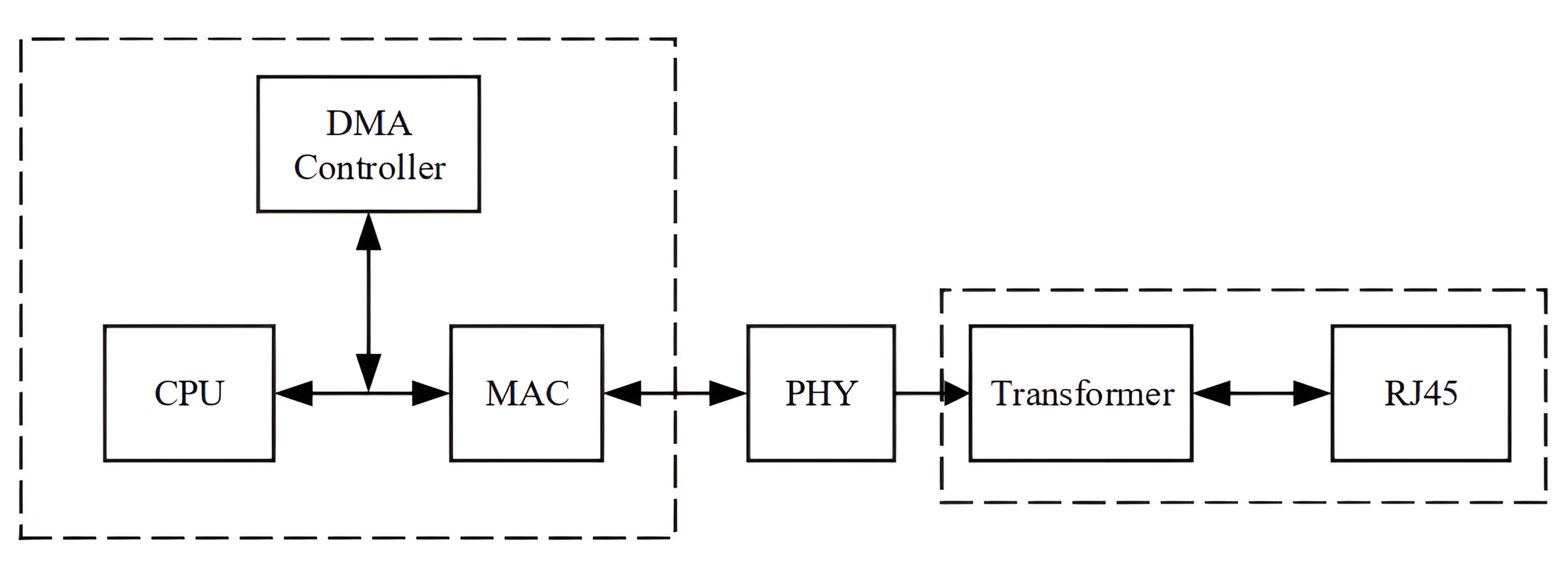

Embedded Ethernet Hardware

The hardware of an embedded system's Ethernet mainly consists of several components: MAC controller, PHY chip, network transformer, RJ45 connector, and in some systems, a DMA controller.

Generally, the CPU/MCU will integrate the MAC on-chip (since the MAC is a digital circuit, it is usually integrated on-chip considering chip area and architecture). Therefore, the hardware that needs to be designed externally is the PHY, transformer, and interface. In many cases, the network transformer is also integrated into the RJ45 connector.

MAC

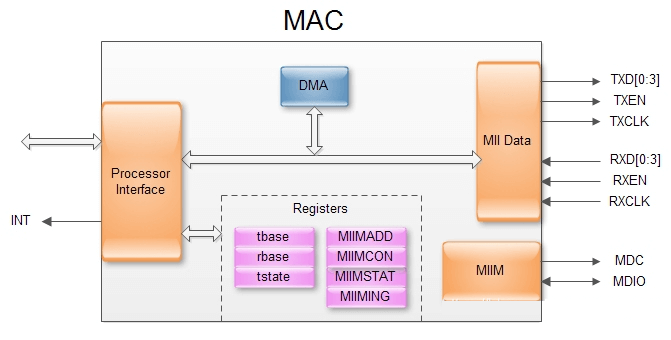

MAC (Media Access Control) is a sublayer protocol of the OSI seven-layer structure, located in the data link layer. It is mainly responsible for controlling and connecting the physical layer medium. MAC follows the IEEE 802.3 standard.

When sending data, the MAC protocol can determine in advance whether data can be sent. If it can be sent, it adds some control information to the data and then sends the data and control information in the specified format to the physical layer.

When receiving data, the MAC protocol first checks the input information and whether transmission errors have occurred. If there are no errors, it removes the control information and sends it to the LLC layer.

PHY

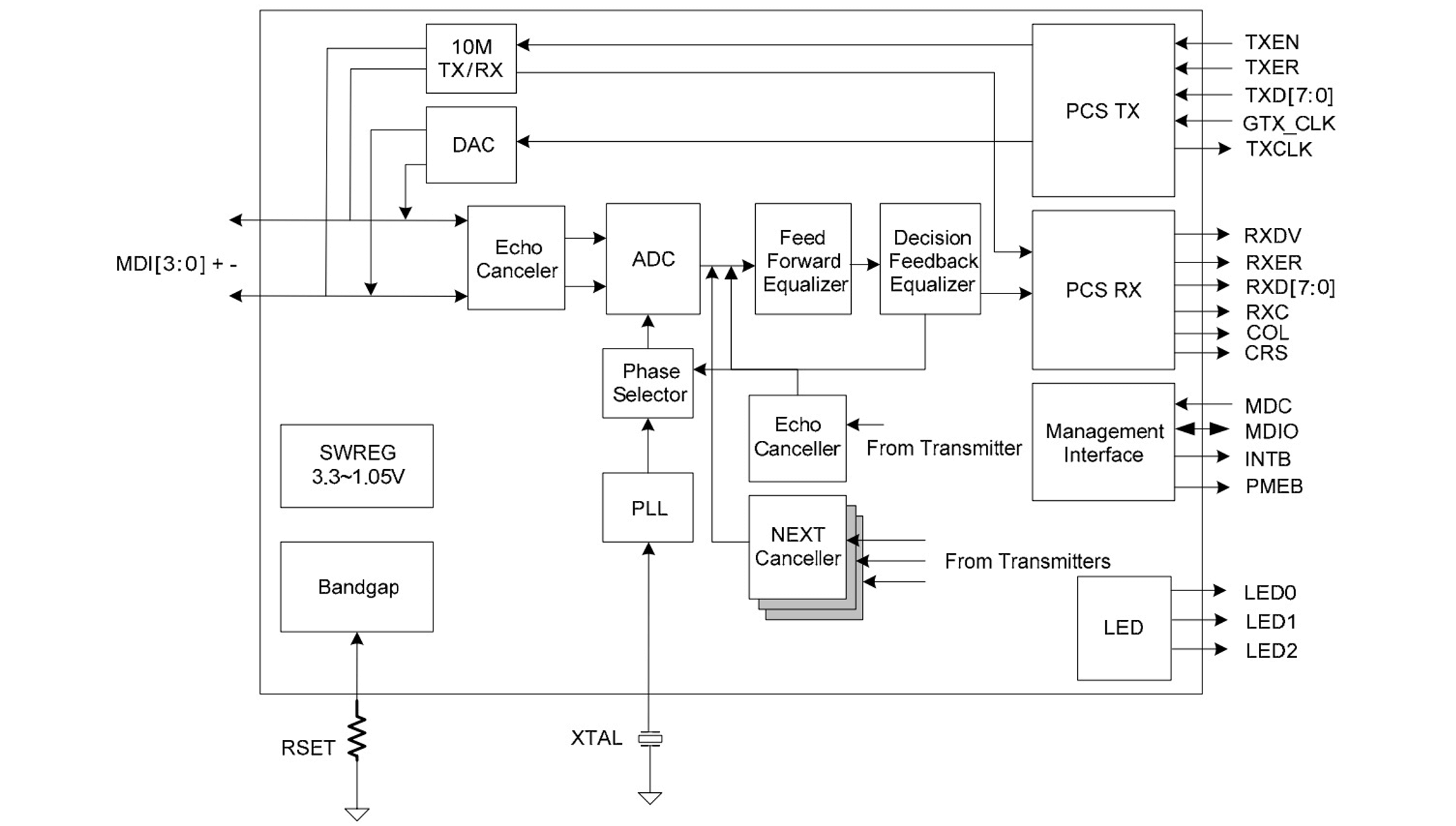

PHY is the physical interface transceiver that implements the physical layer of Ethernet. PHY is defined by the IEEE 802.3 standard and includes the Media Independent Interface (MII)/Gigabit Media Independent Interface (GMII) sublayer, Physical Coding Sublayer (PCS), Physical Medium Attachment (PMA) sublayer, Physical Medium Dependent (PMD) sublayer, and MDI sublayer.

When sending data, PHY receives the data transmitted from the MAC (for PHY, there is no concept of frames, it only sees data regardless of address, data, or CRC. For 100BaseTX, it uses 4B/5B encoding, where every 4 bits adds 1 bit of error detection code). Then, it converts parallel data into serial stream data, encodes the data according to the physical layer's encoding rules, and converts it into analog signals to send out. The process is reversed when receiving data. The typical internal structure diagram of PHY is shown below (RTL8211E):

Interface Protocol between MAC and PHY

This post is translated using ChatGPT, please feedback if any omissions.