Competition and Hazards in Digital Circuits

In digital circuits, there are phenomena of competition and hazards due to the delay in signal transmission and state transitions.

Reasons

- Competition: In combinational logic circuits, when input signals from different paths change and reach the same gate-level circuit, there is a time difference.

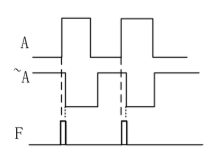

- Hazards: Due to the existence of competition, the output signal takes some time to reach the desired state, and during the transition period, there may be momentary erroneous outputs, such as spike pulses.

Competition does not necessarily lead to hazards, but hazards always involve competition.

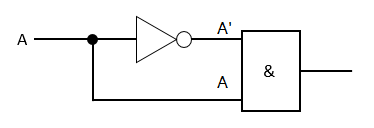

For example, for the same input signal A, the signal A' will be delayed compared to A when it reaches the AND gate due to passing through an inverter, causing interference pulses in the output of the AND gate:

Solutions

The following methods can be used to eliminate hazards:

- Increase output filtering capacitance: Used to eliminate narrow pulses of hazards. However, the drawback is that it smooths out the waveform, making it prone to errors in high-speed signals.

- Delayed reading of output values: Neglect the influence of narrow pulses.

References and Acknowledgements

Original: https://wiki-power.com/

This post is protected by CC BY-NC-SA 4.0 agreement, should be reproduced with attribution.This post is translated using ChatGPT, please feedback if any omissions.