واجهة الاختبار و TIC الأساسية

في اختبار الشرائح النصفية، TIC (وحدة تحكم واجهة الاختبار) هي وحدة تحكم الحافلة الرئيسية التي تتبع بروتوكول واجهة الاختبار الموجود في مواصفات AMBA (بنية الحافلة المتقدمة للمتحكمات الدقيقة المتقدمة). AMBA هي معيار الاتصال على رقاقة للمتحكمات الدقيقة المضمنة وتشمل ثلاثة أنواع من بروتوكولات الحافلة:

- AHB (الحافلة عالية الأداء المتقدمة)

- ASB (الحافلة النظام المتقدمة)

- APB (الحافلة الطرفية المتقدمة)

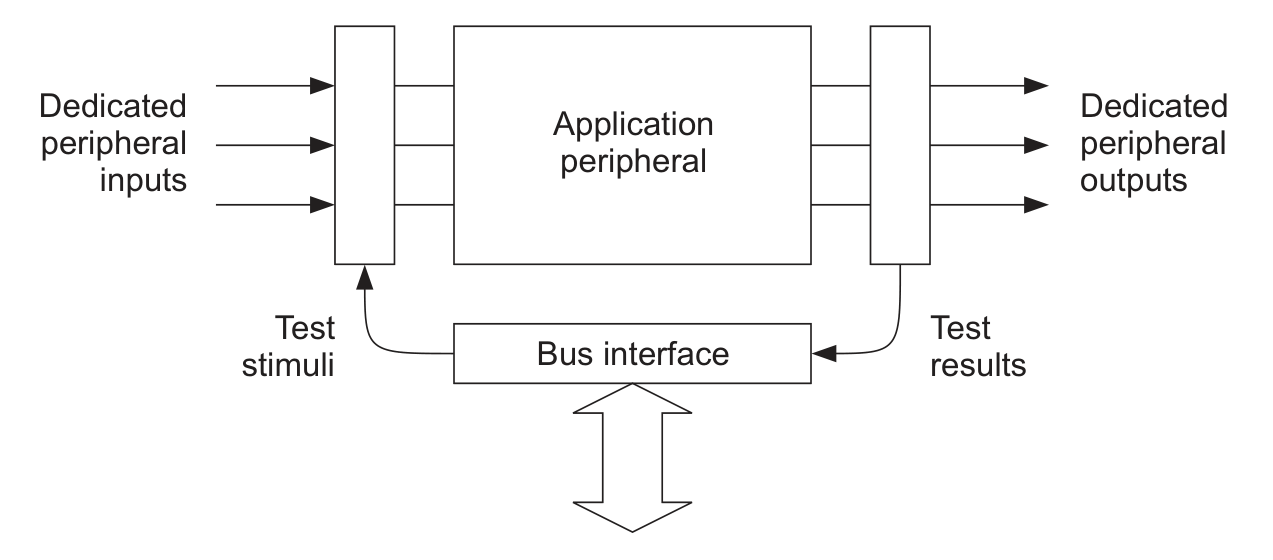

نظرًا لأن فلسفة AMBA تتمحور حول اختبار وحدات النظام بشكل منفصل، فإن اختبار كل وحدة يعتمد فقط على واجهة الحافلة، ويتطلب طريقة اختبار لاختبار إدخالات ومخرجات الأجهزة الطرفية غير المتصلة بالحافلة.

يمكن تحقيق هذه الطريقة باستخدام واجهة الاختبار. تستخدم هذه الواجهة طريقة بسيطة للتحكم في قراءة وكتابة الفيكتور، وتستخدم أيضًا واجهة الحافلة الخارجية (EBI) كمسار للبيانات لاستيراد الفيكتور الخارجي إلى الحافلة الداخلية.

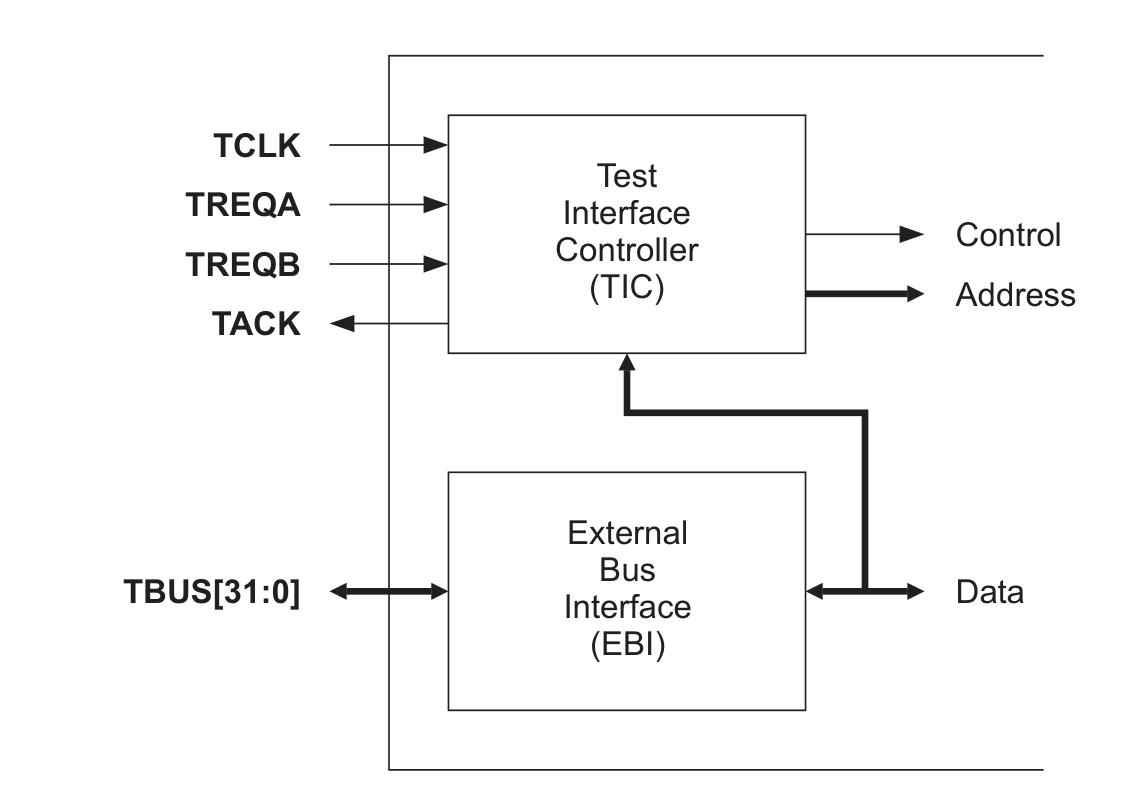

أرجل واجهة الاختبار

من الرسم السابق، يتكون أرجل واجهة الاختبار من ثلاثة أجزاء:

- دبوس ساعة واحد TCLK

- ثلاثة دبابيس تحكم TREQA، TREQB و TACK

- حافلة اختبار بعرض 32 بت TBUS[31:0]

في التكوين الأدنى، تحتاج واجهة الاختبار فقط إلى TREQA و TACK كـ أرجل مخصصة للتحكم في دخول وخروج وضع الاختبار. يمكن تحقيق الأرجل الأخرى عن طريق إعادة استخدام أرجل الجهاز.

TREQA/TREQB (طلب الحافلة للاختبار) هي إشارة مدخلة. أثناء تشغيل النظام العادي، يُستخدم TREQA لطلب دخول وضع الاختبار للسماح بتحميل الفيكتور. أثناء عملية الاختبار، يتم استخدام TREQA و TREQB معًا للإشارة إلى نوع الفيكتور المستخدم في الدورة التالية.

TACK (تأكيد الحافلة للاختبار) هو إشارة مخرجة تُستخدم لتمثيل حالة الحافلة وتشير إلى اكتمال عنصر الاختبار. عندما يكون TACK منخفضًا، يعني ذلك أن الفيكتور الحالي يحتاج إلى وقت إضافي حتى يصبح TACK عاليًا. فقط عندما يكون TACK عاليًا، ستقوم TREQA/TREQB بقراءة إشارات التحكم الخارجية.

TCLK (ساعة الاختبار) هي إشارة ساعة مدخلة. يتم توفير ساعة اختبار واجهة الاختبار من خارج النظام. عند التبديل بين الوضع العادي ووضع الاختبار، يتطلب أن تكون ساعة TCLK خالية من الضوضاء.

TBUS[31:0] (حافلة الاختبار) هي حافلة واجهة اختبار ثنائية الاتجاه بعرض 32 بت. في وضع الإدخال، يُستخدم لنقل عنوان الفيكتور ومعلومات التحكم وتنفيذ الكتابة؛ في وضع الإخراج، يمكن استخدامه لتنفيذ القراءة. عند الحاجة إلى تغيير حالة إدخال/إخراج TBUS، يضمن بروتوكول الحافلة الاختبار توفير دورة للتبديل.

عند تشغيل النظام بشكل طبيعي، يكون جدول الحقيقة المتحكم فيه بواسطة ثلاثة أسلاك كما يلي:

| TREQA | TREQB | TACK | الحالة |

|---|---|---|---|

| 0 | 0 | 0 | يعمل بشكل طبيعي ، لم يتم دخول وضع الاختبار |

| 1 | 0 | 0 | طلب الدخول إلى وضع الاختبار |

| 0 | 1 | 0 | محجوزة لطلب المضيف الخارجي |

| - | - | 1 | تم دخول وضع الاختبار |

في البداية ، يكون TREQA على مستوى منخفض ، مما يعني أنه لم يتم دخول وضع الاختبار بعد. عندما يتم تعيين TREQA على مستوى عالٍ ، يتم طلب الدخول إلى وضع الاختبار. ثم ، عندما يكون TACK على مستوى عالٍ ، يعني أن TIC يسمح بالدخول إلى وضع الاختبار. في هذه الحالة ، يصبح TCLK مصدر الساعة الداخلية. بمجرد الدخول إلى وضع الاختبار ، تكون القيم على الثلاثة خطوط وحالة النظام كما يلي:

| TREQA | TREQB | TACK | الحالة |

|---|---|---|---|

| - | - | 0 | العملية الحالية لم تكتمل بعد |

| 1 | 1 | 1 | Address/Control/TurnAround Vector |

| 1 | 0 | 1 | Write Test Vector |

| 0 | 1 | 1 | Read Test Vector |

| 0 | 0 | 1 | الخروج من وضع الاختبار |

بعد ذلك ، يمكن تعيين TREQB على مستوى عالٍ لتحميل Address Vector. بعد ذلك ، يمكن القيام بعمليات القراءة والكتابة. عند الحاجة إلى الخروج من وضع الاختبار ، يجب تمرير Address Vector أولاً للتأكد من اكتمال جميع عمليات النقل الداخلية. ثم يتم تعيين كل من TREQA و TREQB على مستوى منخفض ، مما يعني الخروج من وضع الاختبار. في النهاية ، سيتم إخراج TACK على مستوى منخفض ، مما يعني الخروج من وضع الاختبار.

أنواع الـ Vector

في واجهة الاختبار ، هناك 5 أنواع من الـ Vector:

- Address Vector: Vector يعلن العنوان

- Write Test Vector: Vector للكتابة (0/1)

- Read Test Vector: Vector للقراءة (L/H)

- Control Vector: Vector للتحكم

- TurnAround Vector: Vector للتبديل

تتم تحديد تنشيط Address/Control/TurnAround Vector بناءً على قيم مشتركة لـ TREQA/TREQB. يمكن تحديد نوع الـ Vector وفقًا للقواعد التالية:

- إذا ظهرت فقط عبارة واحدة من Address/Control/TurnAround Vector: فإنها تكون Address Vector.

- إذا ظهرت سلسلة متواصلة من Address/Control/TurnAround Vector: باستثناء العبارة الأخيرة التي تكون Control Vector ، فإنها تكون جميعها Address Vector.

- بعد عبارة واحدة أو أكثر من Read Vector: ستتبعها دائمًا عبارة TurnAround Vector. (في ASB ، يكون واحدًا فقط ، في حين أن AHB يحتاج إلى اثنين)

بالإضافة إلى ذلك ، يتم دمج عبارات الـ Write/Read Test Vector المتعددة في Burst Vector (لاحظ أنها نفس النوع فقط ، ليست مختلطة). بذلك ، يتم تطبيق العنوان مرة واحدة فقط ، مما يسرع عملية الاختبار. يمكن أن يكون هذا العنوان ثابتًا (جميع الـ Vector تستخدم نفس العنوان الأصلي المرسل) أو يمكن أن يكون عنوانًا تصاعديًا (يعتمد على ما إذا كان هناك مضاعف عناوين ممكّن في TIC). في حالة عدم وجود مضاعف عناوين ، سيتم استخدام العنوان الثابت افتراضيًا.

Address Vector

في أي عملية قراءة / كتابة ، يجب تمرير Address Vector أولاً. يتبع القاعدة التالية:

- يجب تعيين TREQA / TREQB إلى 1 للإشارة إلى أن الدورة التالية هي Address Vector.

- في الدورة التالية ، يتم تحميل العنوان على TBUS [31: 0]. في هذا الوقت ، ستحدد القيم الموجودة على TREQA / TREQB حالة الدورة التالية.

في بعض أنظمة الإشارات السريعة ، قد يكون من الضروري تحميل عدة Address Vector متتالية (زيادة الوقت الكافي لنقل العنوان من الخارج إلى الحافلة الداخلية للعنوان). في هذه الحالة ، ستكون TACK في TIC 0 في إخراج Address Vector الأول لفرض تحميل الدورة الثانية لعنوان Vector.

Control Vector

سيتم دائمًا تتبع Control Vector بعد Address Vector أو سلسلة من Address Vector ، ويستخدم لتحديث معلومات التحكم الداخلية في TIC. يتبع القاعدة التالية:

- يجب تعيين TREQA / TREQB إلى 1 للإشارة إلى أن الدورة التالية هي Address Vector.

- في الدورة التالية ، يتم تحميل العنوان على TBUS [31: 0]. في هذا الوقت ، ستظل القيم الموجودة على TREQA / TREQB 1 ، وسيظهر Control Vector في الدورة التالية.

- في الدورة التالية ، ستتم تحميل معلومات التحكم على TBUS [31: 0]. في هذا الوقت ، ستحدد القيم الموجودة على TREQA / TREQB حالة الدورة التالية.

إذا كان من الضروري تعيين Control Vector غير صالح ، فيمكن تعيين البت 0 إلى 0 ، وبالتالي يمكن الاحتفاظ بمعلومات Control Vector ولكن لا يتم تطبيقها.

Write Test Vector

بمجرد دخول وضع الاختبار بنجاح وتحديد العنوان ، يمكنك القيام بعمليات القراءة / الكتابة. يتم تحديد العنوان المستخدم في عملية الكتابة بواسطة Address Vector السابق. يمكن أن يتبع Write Test Vector الأنواع التالية من الناحية النظرية:

- Address Vector واحد فقط.

- سلسلة من Address / Control Vector.

- Write Test Vector آخر. تشكل سلسلة Write Burst.

- TurnAround Vector بعد عملية قراءة مرة واحدة / متعددة.

عندما يكون الحالة نشطة ، ستصبح TACK منخفضة. خلال هذه الفترة ، يجب أن تتغير TREQA / TREQB لتحديد نوع الناقل التالي ، ولكن يجب أن تستمر عملية الكتابة التي تتم على TBUS [31: 0] ولا يجب القيام بعمليات القراءة في هذا الوقت.

Read Test Vector

مثل Write Test Vector ، يتم تحديد العنوان المستخدم في عملية القراءة بناءً على الناقل السابق ، ويمكن أن يتبع Read Test Vector الأنواع التالية من الناحية النظرية:

- Address Vector واحد فقط.

- سلسلة من Address / Control Vector.

- Read Test Vector آخر. تشكل سلسلة Read Burst.

- عملية كتابة مرة واحدة / متعددة.

بعد عملية قراءة مرة واحدة أو متعددة ، يجب أن يكون هناك دائمًا TurnAround Vector لمنع تعارض إشارة TBUS الخارجية.

TurnAround Vector

يمكن استخدام TurnAround Vector لتغيير اتجاه نقل TBUS عند التبديل بين عمليات الكتابة / القراءة. عندما يتحول القراءة إلى كتابة ، فمن الضروري إدراج TurnAround Vector. هذا الإجراء لن يكتب عنوانًا جديدًا.

هذه هي بعض المعلومات الأساسية حول واجهة الاختبار و TIC. بالنسبة لكيفية عمل TIC على AHB بشكل محدد ، يرجى الرجوع إلى المقالة التالية TIC على AHB (قيد الكتابة ...) .

المراجع والشكر

- IHI0011 - ARM advanced microcontroller bus architecture (AMBA) specification.Rev 2.0

عنوان النص: https://wiki-power.com/

يتم حماية هذا المقال بموجب اتفاقية CC BY-NC-SA 4.0، يُرجى ذكر المصدر عند إعادة النشر.تمت ترجمة هذه المشاركة باستخدام ChatGPT، يرجى تزويدنا بتعليقاتكم إذا كانت هناك أي حذف أو إهمال.