أساسيات اختبار الواجهة النصفية - اختبار المعلمات التي تعتمد على التيار المباشر (DC)

اختبار المعلمات التي تعتمد على التيار المباشر (DC) يركز بشكل رئيسي على بعض الخصائص لمفتاح النصفيات على مستوى سلك واحد. فيما يتعلق بمعظم المعلمات التي تعتمد على التيار المباشر (DC)، يتم قياس المقاومة الكهربائية للنصفيات بشكل أساسي، وتوضيح المقاومة الكهربائية يستخدم قانون أوم. إذا كان هناك حاجة للتحقق من قابلية تنفيذ إجراءات اختبار المعلمات التي تعتمد على التيار المباشر (DC)، يمكن أيضًا استخدام مقاومة ثنائية الاتجاه كبديل لمفتاح النصفيات بغرض استبعاد المشكلات التي تكون خارجة عن نطاق مفتاح النصفيات. كمثال، عندما يتعلق الأمر بمعلمة VOL المذكورة في كتيب المواصفات للشريحة:

| المعلمة | الوصف | شروط الاختبار | الحد الأدنى | الحد الأقصى | الوحدات |

|---|---|---|---|---|---|

| VOL | جهد الإخراج الأدنى | VDD = الحد الأدنى, IOL = 8.0 مللي أمبير | 0.4 | فولت |

نلاحظ أن قيمة VOL القصوى هي 0.4 فولت، و IOL هي 8 مللي أمبير، وهذا يعني أنه يجب أن يتم إنتاج تيار بقوة 8 مللي أمبير في جهد لا يزيد عن 0.4 فولت عندما يكون المستوى الكهربائي منخفضًا بشكل منطقي. بناءً على ذلك، يمكننا التوصل إلى أن المقاومة الكهربائية القصوى لهذا المفتاح لا تتجاوز 50 أوم. لذلك، يمكن استخدام مقاومة ثنائية الاتجاه التي لا تتجاوز 50 أوم كبديل لاختبار عمليات الاختبار. هدفنا هو تركيز المشكلة على مفتاح النصفيات نفسه، وليس على مشكلات خارجية تتعلق بمفتاح النصفيات.

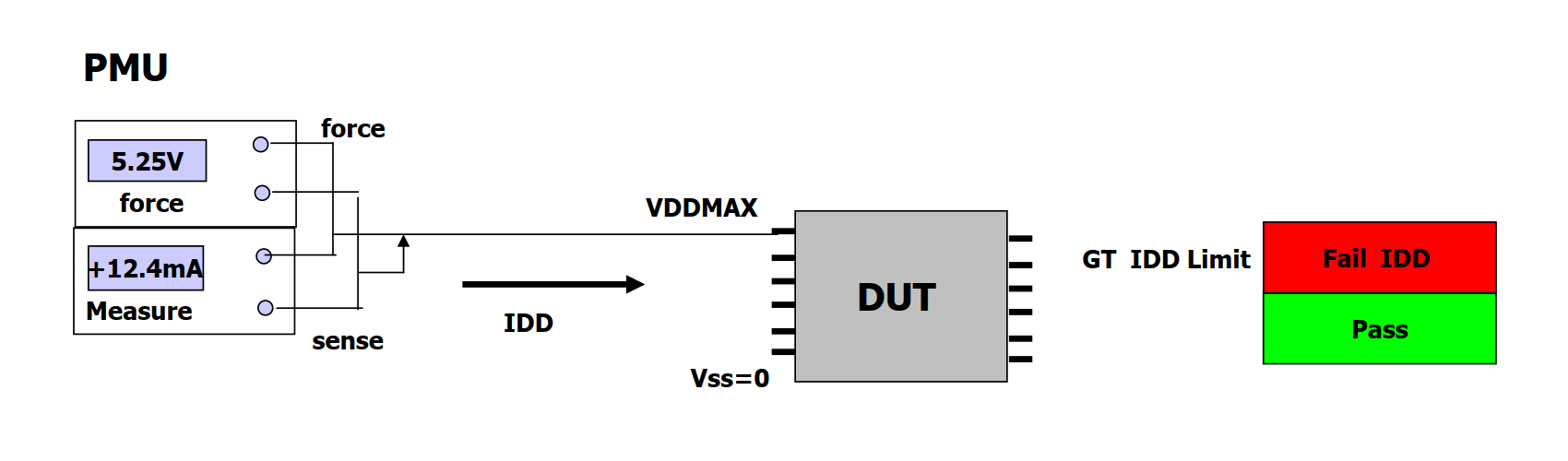

IDD وGross IDD

تمثل معلمة IDD التي تعتمد على التيار المباشر (DC) التيار الكهربائي الذي يتدفق من تسريب (D) إلى تسريب (D) في الدائرة الكهربائية CMOS (أو يُعرف باسم ICC إذا كان الدائرة TTL). يشير مصطلح Gross IDD إلى الإجمالي الذي يتدفق إلى دبوس VDD (ويمكن اختباره سواء في مرحلة Wafer Probe أو في مرحلة المنتج النهائي). يتم استخدام اختبار IDD للتحقق مما إذا كان التيار الكهربائي الإجمالي للشريحة يتجاوز الحدود المحددة. وعادةً ما يتعين مراجعة التيار الكهربائي في أقل استهلاك للطاقة وتردد عمل أقصى.

يتم اختبار Gross IDD لتحديد ما إذا كان بإمكاننا متابعة اختبار مفتاح النصفيات أم لا. عادةً ما يتم إجراء اختبار Gross IDD مباشرة بعد اختبار النظام العام (OS) وهو أول اختبار يتم بعد تشغيل مفتاح النصفيات. إذا لم يتم اجتياز اختبار Gross IDD (على سبيل المثال، إذا كان التيار كبيرًا جدًا)، فإنه لا يمكن المضي قدمًا في الاختبار.

خلال مرحلة اختبار Gross IDD، لا نعرف بعد ما إذا كان بإمكان الإعداد الأولي أن يتم بنجاح، لذا يتعين علينا تخفيف المواصفات لمعلمة IDD. بعد اجتيا

1. استخدم متجهات الاختبار لضبط DUT لاستهلاك أدنى للتيار والحفاظ على حالة السكون.

2. قم بقياس قيم التيار على الأقطاب

- أعلى من IDD المحدد: فشل

- غير ذلك: نجاح

عند القيام بالاختبار عادة ما يتعين تضمين تأخير بين التشغيل وعملية الأخذ للسماح للسعة الكهرواستاتية بالشحن بشكل كامل وتجنب التداخل.

إذا كنت بحاجة إلى اختبار تيار ساكن مختلف وفقًا لتكوينات منطقية مختلفة، يمكنك اختبار معامل IDDQ لزيادة نطاق الاختبار (IDDQ هو قياس للتيار في حالة منطقية ثابتة معينة، على سبيل المثال تشغيل أجزاء من MOSFET في حالة معينة).

### اختبار IDD - الأسلوب الدينامي

هدف اختبار IDD الدينامي هو اختبار DUT أثناء تنفيذ وظيفته بشكل دينامي (عادة عند أقصى تردد للعمليات) لضمان أنه لا يتجاوز القيمة المحددة.

لنأخذ مثالًا، الجدول التالي يوضح عينة من معلمات IDD الدينامي:

| المعلمة | الوصف | ظروف الاختبار | الحد الأدنى | الحد الأقصى | الوحدة |

| ----------- | ----------------- | ------------------------------------ | ----------- | ----------- | ---------- |

| IDD Dynamic | تيار إمداد الطاقة | VDD = 5.25V (تجاري)، f=f_max (66MHz) | | +18 | مللي أمبير |

مخطط الاختبار:

العملية الاختبارية مشابهة للأسلوب الثابت.

## VOL/IOL وVOH/IOH

VOL تعبر عن أعلى جهد للإخراج عند مستوى منخفض (L) (لا يتعرف على أنه منطق 1). IOL تعبر عن قدرة الدفع للتيار العابر (I، إغراق) عند الإخراج على مستوى منخفض (L). يتم قياس مقاومة الأقطاب بشكل مشترك لضمان قدرتها على استيعاب تيار ثابت تحت جهد مناسب.

VOH تعبر عن أدنى جهد للإخراج عند مستوى مرتفع (H) (لا يتعرف على أنه منطق 0). IOH تعبر عن قدرة الدفع للتيار السابق (I، مصدر) عند الإخراج على مستوى مرتفع (H). يتم قياس مقاومة الأقطاب بشكل مشترك لضمان قدرتها على إخراج تيار ثابت تحت جهد مناسب.

لنأخذ مثالًا، الجدول التالي يوضح معلمات VOL/IOL وVOH/IOH لذاكرة الوصول العشوائي الثابتة بسعة 256x4:

| المعلمة | الوصف | ظروف الاختبار | الحد الأدنى | الحد الأقصى | الوحدة |

| ------- | ------------------ | ---------------------------------- | ----------- | ----------- | ------ |

| VOL | جهد الإخراج الأدنى | VDD = 4.75V، IOL = 8.0 مللي أمبير | | 0.4 | فولت |

| VOH | جهد الإخراج الأعلى | VDD = 4.75V، IOH = -5.2 مللي أمبير | 2.4 | | فولت |

اختبار VOL/IOL وVOH/IOH يتم بشكل رئيسي للتحقق مما إذا كانت VOL/VOH في المستوى الصحيح عند تطبيق تيار إغراق أو تيار مصدر، وذلك لضمان قدرتها على إخراج الجهد المناسب تحت تيار محدد. هناك طريقتان للاختبار: الأسلوب الثابت والأسلوب الدينامي. \*\*الأسلوب الثابت يشمل تطبيق التيار على الأقطاب ثم قياس الجهد تدريجياً، بينما الأسلوب الدينامي يشمل توفير VREF أثناء الاختبار الوظيفي لإنشاء تيار تحميل دي

- IOL هو قيمة تيار إيجابي لأنه يتدفق من PMU إلى DUT.

- نظرًا لأن تم تطبيق تيار ثابت، يجب ضبط مشبك الجهد، وإذا تم قياس الجهد وكان أقل من جهد المشبك، قد يكون السبب أن الإشارة معدة على مستوى عال، مما يؤدي إلى تنشيط الصمام الثنائي لحماية الطاقة في اتجاه إيجابي.

- المعامل VDDmin يمثل الحد الأدنى للجهد المزود الذي يجب توفيره لـ DUT لضمان أن الاختبار يتم بنجاح، وفي حالة الجهد أقل من هذا الحد، فإن النتائج لن تكون دقيقة.

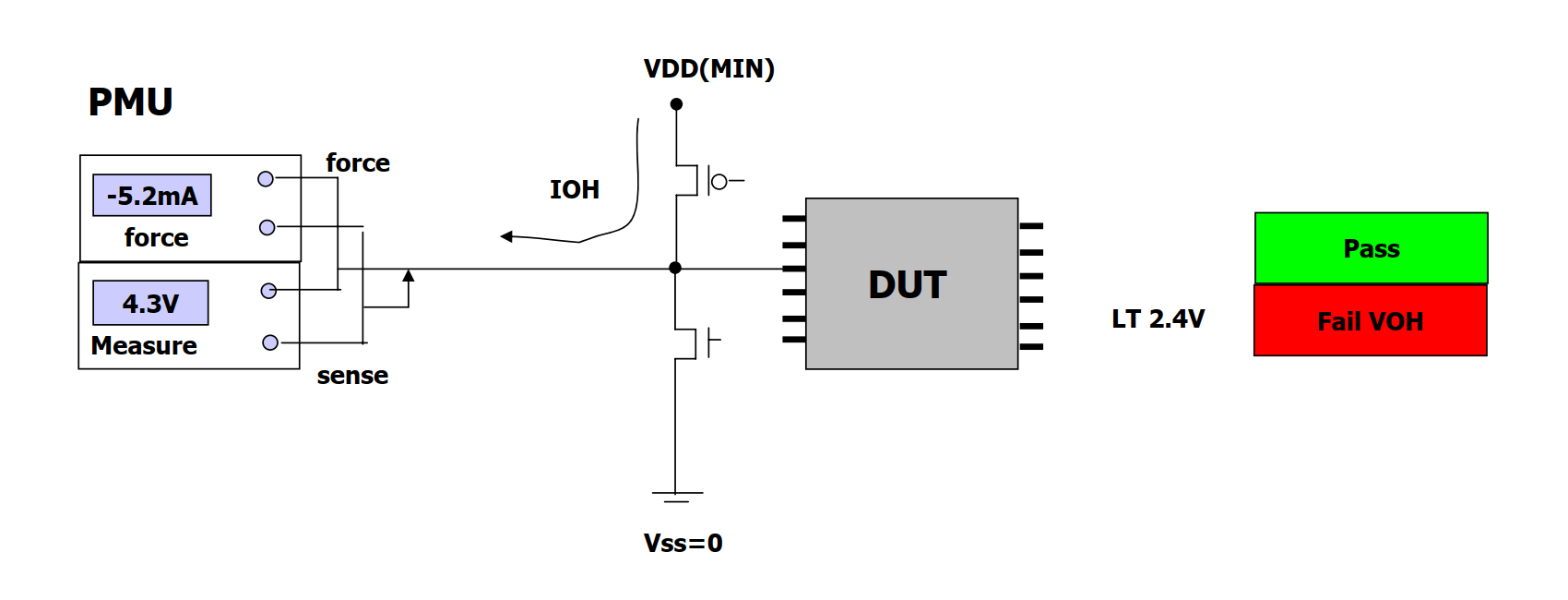

### اختبار VOH/IOH - الأسلوب الثابت التسلسلي

يمكن رؤية الشكل التوضيحي أدناه لقياس اختبار VOH/IOH باستخدام الأسلوب الثابت التسلسلي:

يمكن تقديم الاختبار كالتالي:

1. يجب أن يتم تعيين دبوس الاختبار كمستوى عال أولاً باستخدام معالجة مسبقة.

2. ثم يتم تطبيق تيار IOH ثابت على الدبوس، مع انتظار مدة تتراوح بين 1 و 5 ميلي ثانية (تم تعيين الانتظار في PMU).

3. يجب فحص جهد الدبوس:

- إذا كان أقل من VOH (+2.4V): يتم اعتبارها فشل.

- في الحالات الأخرى: تعتبر ناجحة.

أمور يجب مراعاتها:

- نظرًا لأن IOL يتدفق من PMU إلى DUT، فإنه يكون قيمة سلبية.

- بسبب تطبيق تيار ثابت، يجب ضبط مشبك الجهد، وإذا تم قياس الجهد وكان أعلى من جهد المشبك، قد يكون السبب أن الإشارة معدة على مستوى منخفض، مما يؤدي إلى تنشيط الصمام الثنائي لحماية الأرض بشكل إيجابي.

- المعامل VDDmin يمثل الحد الأدنى للجهد المزود الذي يجب توفيره لـ DUT لضمان أن الاختبار يتم بنجاح، وفي حالة الجهد أقل من هذا الحد، فإن النتائج لن تكون دقيقة.

## IIL/IIH

يشير IIL إلى أقصى تيار انسحاب (من الخارج عبر الدبوس إلى الأرض VSS لـ DUT) المسموح به عندما يكون إشارة الدخول (I) منخفضة (L). وهذا يستخدم لمراقبة ما إذا كانت أشارة الدخول تتجاوز الحدود الكهربائية ولقياس درجة العزل. أما IIH، فيشير إلى أقصى تيار إمداد (من VDD لـ DUT عبر الدبوس إلى الخارج) المسموح به عندما تكون إشارة الدخول (I) عالية (H). على سبيل المثال، فيما يلي معلومات حول معاملات IIL وIIH لذاكرة الوصول العشوائي الثابتة 256 × 4:

| المعامل | الوصف | شروط الاختبار | الحد الأدنى | الحد الأقصى | الوحدات |

| -------- | ------------------ | ----------------------- | ----------- | ----------- | ------- |

| IIL، IIH | تيار الحمل الداخلي | Vss ≤ Vin ≤ VDD (5.25V) | -10 | +10 | µA |

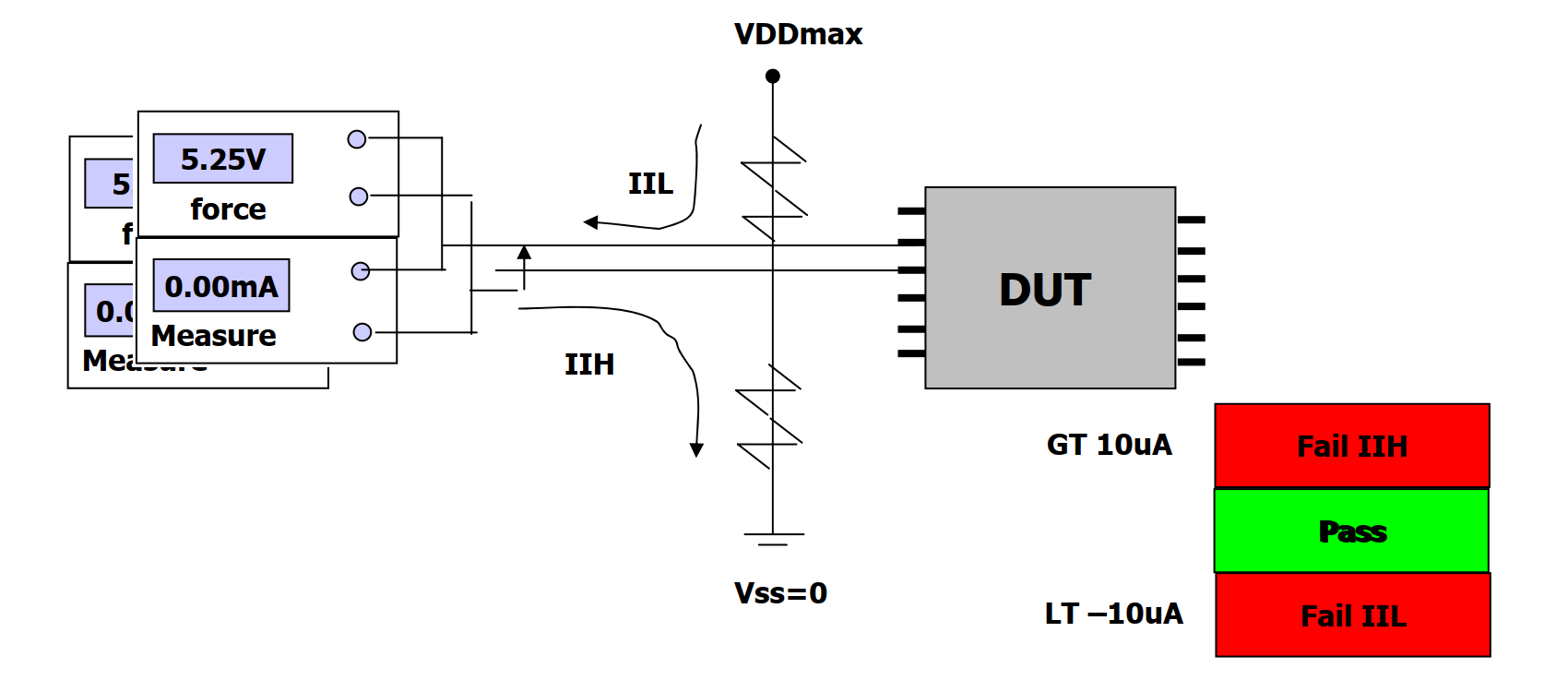

يتم قياس IIL لقياس المقاومة بين دبوس الإدخال و VDD. بينما يتم قياس IIH لقياس المقاومة بين دبوس الإدخال و VSS. يتم تنفيذ اختبار IIL/IIH بأساليب تسلسلية، متوازية أو مدمجة، أو بأساليب اختبار وظائف أخرى. الاختبار التسلسلي يتطلب وقتًا إضافيًا نسبيًا ولكنه دقيق.

بالإضافة إلى ذلك، يجب أن يتم تنفيذ اختبار IIL

في بعض أنظمة الاختبار، يمكن قياس تسرب التيار المتوازي (Parallel Test Method). تسرب التيار المتوازي يتضمن قياس تسرب التيار لعدة دبابيس باستخدام عدة وحدات قياس PMU. يتم جعل جميع دبابيس الإدخال عالية الجهد بشكل متزامن ومن ثم يتم قياس تيار كل دبوس على حدة بشكل متزامن. ثم يتم مقارنة النتائج مع القيم المعيارية للتوصل إلى الاستنتاج.

1. يجب أن يتم توفير مصدر طاقة VDDmax للجهاز تحت الاختبار DUT.

2. استخدام عدة وحدات PMU لجعل جميع دبابيس الإدخال عالية الجهد إلى VDDmax (قياس IIH).

3. انتظار مدة تتراوح بين 1 و 5 ميكروثانية، ثم يتم قياس التيار وإجراء المقارنة للوصول إلى الاستنتاج.

4. ثم يتم جعل الدبابس منخفضة الجهد إلى VSS ويتم تكرار الخطوات السابقة لقياس IIL.

الميزة الرئيسية للأسلوب المتوازي هي القدرة على قياس تيار كل دبوس بشكل فردي والقيام باختبار IIL/IIH بشكل سريع. ومن العيوب أنه من الصعب كشف تسرب بين الدبابيس بسبب أن جميع الإدخالات تُحافظ على نفس المستوى.

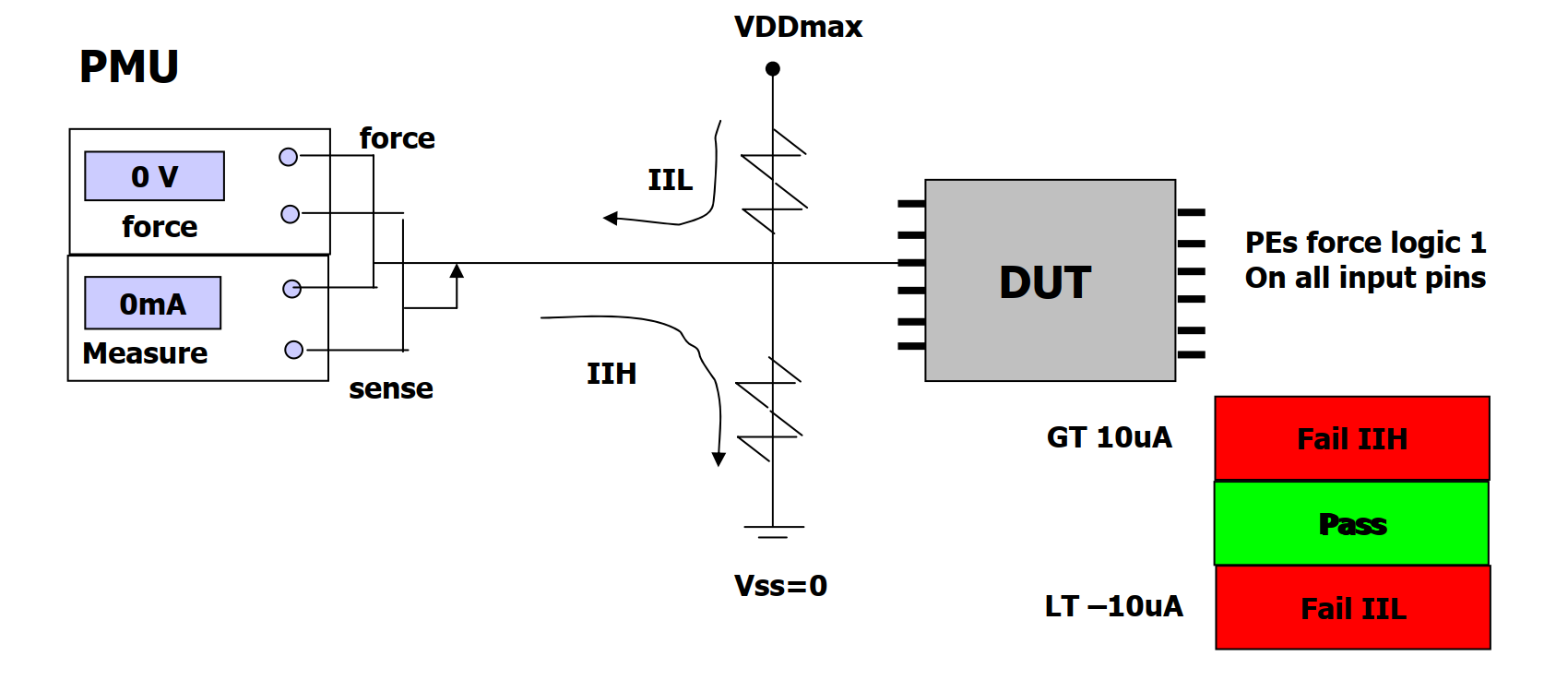

### اختبار IIL/IIH - طريقة الجمع الثابت

تشير طريقة الجمع (Ganged Method) إلى دمج جميع دبابيس الإدخال إلى دبوس واحد واستخدام وحدة PMU واحدة لقياس إجمالي تسرب التيار. الرسم التوضيحي للاختبار كما يلي:

الطريقة المجتمعة مشابهة للأسلوب السابق. الحد الأقصى للتيار المسموح به هو قيمة الدبوس الفردي المعيارية. إذا كانت النتائج تتجاوز الحدود المسموح بها، يجب إعادة الاختبار بالطريقة المتسلسلة. هذا الاختبار يعمل بشكل جيد على أجهزة CMOS (إدخالات ذات مقاومة عالية).

## IOZL/IOZH

تشير IOZ الكهربائية العالية إلى تسرب التيار على دبوس الإخراج (O) عند حالة عالية المقاومة (Z). حيث يشير IOZL إلى تسرب التيار عندما يكون الدبوس في حالة منخفضة (L)، وIOZH يشير إلى تسرب التيار في حالة عالية (H). يُستخدم للتحقق مما إذا كانت هناك تجاوزات في تسرب التيار أثناء إغلاق الدبوس.

هذا المعلمة هامة لضمان أن "دبابيس الإخراج ذات الاتجاهين أو العالية المقاومة يمكنها أن تُغلق بشكل صحيح (حالة ذات مقاومة عالية)". يتم تمثيل هذا في وثيقة المواصفات عادة على النحو التالي:

| المعلمة | الوصف | شروط الاختبار | الحد الأدنى | الحد الأقصى | الوحدات |

| ------- | ----------------------------------- | ---------------------------------- | ----------- | ----------- | ------- |

| IOZ | تيار الإخراج في حالة عالية المقاومة | VSS ≤ Vout ≤VDD(5.25V), إخراج معطل | -2.0 | +2.0 | µA |

### اختبار IOZL/IOZH - الطريقة الثابتة التسلسلية

الرسم التوضيحي لاختبار IOZL/IOZH التسلسلي الثابت كما يلي:

عملية الاختبار تتضمن الخطوات التالية:

1. أولاً، يجب توفير مصدر طاقة VDD للجهاز.

2. يتم

| المعامل | الوصف | شروط الاختبار | الحد الأدنى | الحد الأقصى | الوحدات |

| ------- | ---------------- | --------------------------------------- | ----------- | ----------- | ------- |

| VI | جهد مشبك الإدخال | VCC = الحد الأدنى، Iin = -18 مللي أمبير | | +1.5 | فولت |

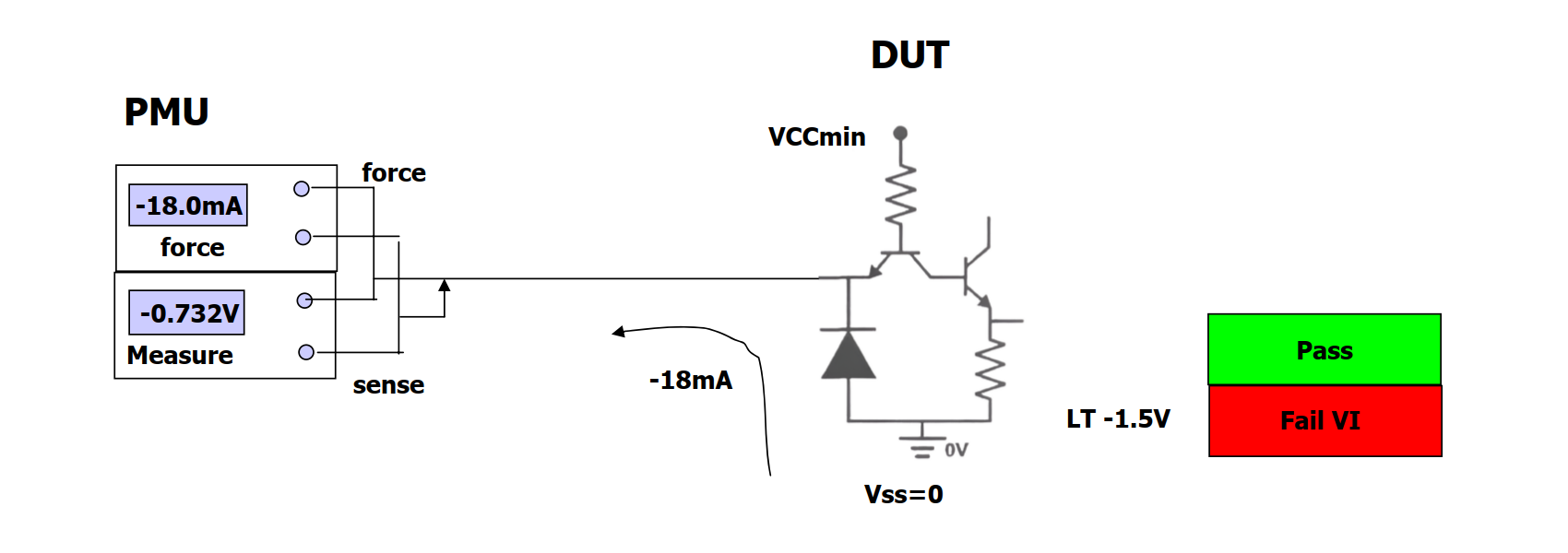

### اختبار VI - الأسلوب الساكن المتسلسل

يتضمن اختبار VI الأسلوب الساكن المتسلسل تصور اختباري كما هو موضح أدناه:

إليك خطوات الاختبار:

1. تأكد أولاً من أن هذا هو دبوس إدخال جهاز TTL ، ثم قم بتوصيله بجهد VCCmin.

2. بعد تعيين مشبك الجهد ، استخدم وحدة قياس الطاقة (PMU) لاستخراج تيار يتراوح بين -15 مللي أمبير إلى -20 مللي أمبير.

3. قم بقياس الجهد على الدبوس:

- إذا كان أقل من VI (-1.5 فولت): فشل

- في حالة أخرى: نجاح

## IOS (تيار اختبار الدائرة القصيرة)

تمثل تيار اختبار الدائرة القصيرة الكهربائي المولد عندما يتم توصيل الدبوس الإخراجي (O) في ظروف القصر (S) بالأرض (0V). الغرض من هذا الاختبار هو \*\*قياس المعاوقة الكهربائية للمخرج عندما يكون الإخراج عالي الجهد ويتم قصره إلى صفر الجهد، لضمان أن تيار الإخراج لن يكون كبيرًا جدًا في أسوأ حالة للحمل. كما يعكس أيضًا قدرة دبوس الجهاز الاختباري على شحن الحمل السعوي بأقصى تيار لحظي، ويمكن استخدامه لحساب الزمن الصاعد. يتم تعريف تيار اختبار الدائرة القصيرة IOS في ورقة المواصفات على النحو التالي:

| المعامل | الوصف | شروط الاختبار | الحد الأدنى | الحد الأقصى | الوحدات |

| ------- | --------------------------- | ----------------------------------------------------------------------------------------- | ----------- | ----------- | ---------- |

| IOS | تيار اختبار الدائرة القصيرة | Vout = 0V، VDD = 5.25V، \*يتم توصيل دبوس واحد فقط في وقت واحد لمدة لا تزيد عن ثانية واحدة | -85 | -30 | مللي أمبير |

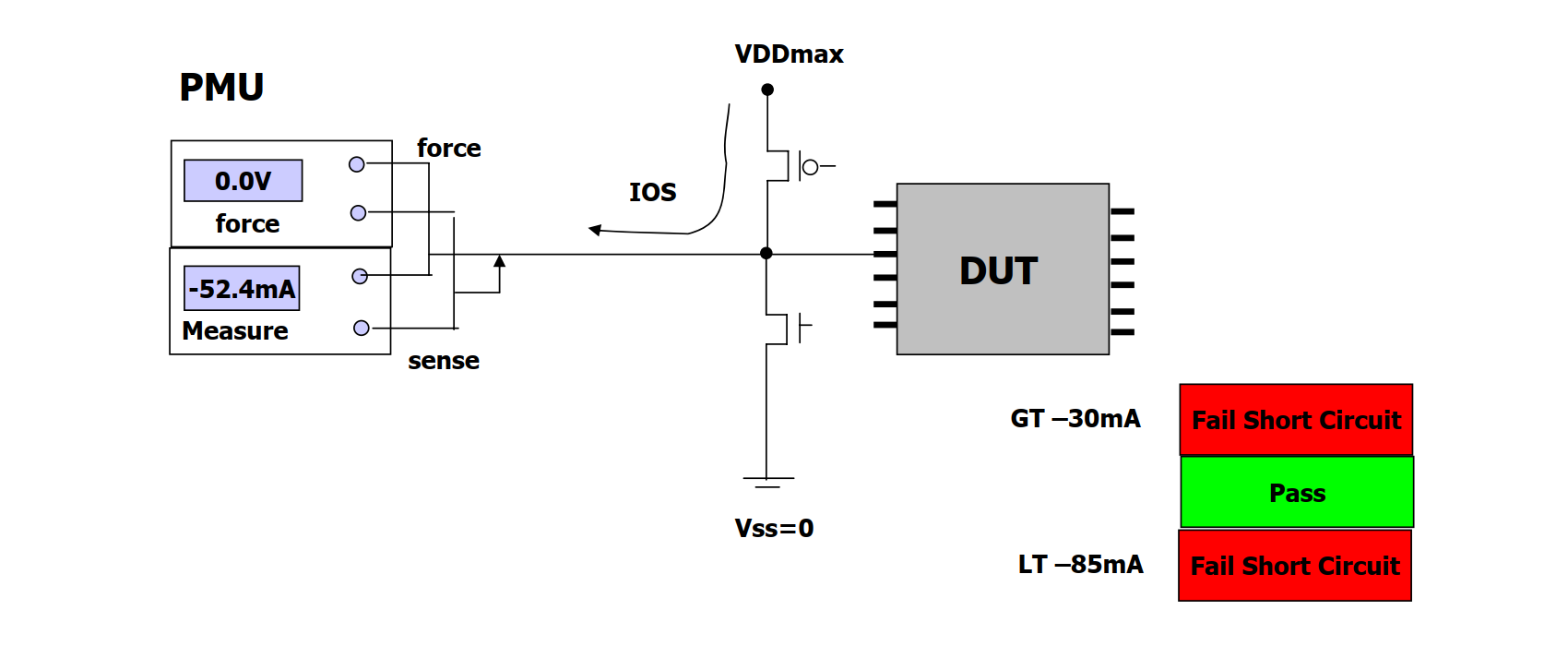

### اختبار IOS - الأسلوب الساكن المتسلسل

تتضمن أسلوب اختبار IOS الساكن المتسلسل تصور اختباري كما هو موضح أدناه:

إليك خطوات الاختبار:

1. قم بتوصيل الجهد VDDmax وقم بإعداد الجهاز مسبقًا بحيث يكون الإخراج عالي الجهد.

2. استخدم وحدة قياس الطاقة (PMU) لجعل الدبوس منخفض الجهد إلى 0V، ثم قم بقياس تيار الإخراج وقارنه بالقيمة المحددة، وقرر النتيجة.

في اختبار IOS ، يجب أن يتم التبديل بعناية لتجنب التحول الحراري. يجب أن يتم تعيين وحدة قياس الطاقة أولاً إلى وضع قياس الجهد بقيمة صفرية محددة ومتصلة بالإخراج للجهاز تحت الاختبار. يجب أن يتم قياس والاحتفاظ بجهد VOH للجهاز تحت الاختبار، ثم قم بفصل الاتصال وقم بتعيين وحدة قياس الطاقة لجعل الجهد عالي الجهد الذي تم قياسه للتو (VOH) ثم قم بإعادة الاتصال بالجهاز (وفي هذا الوقت يكون الجهد على كلا الجانبين VOH) ومن ثم جعل وحدة قياس الطاقة منخفضة ال

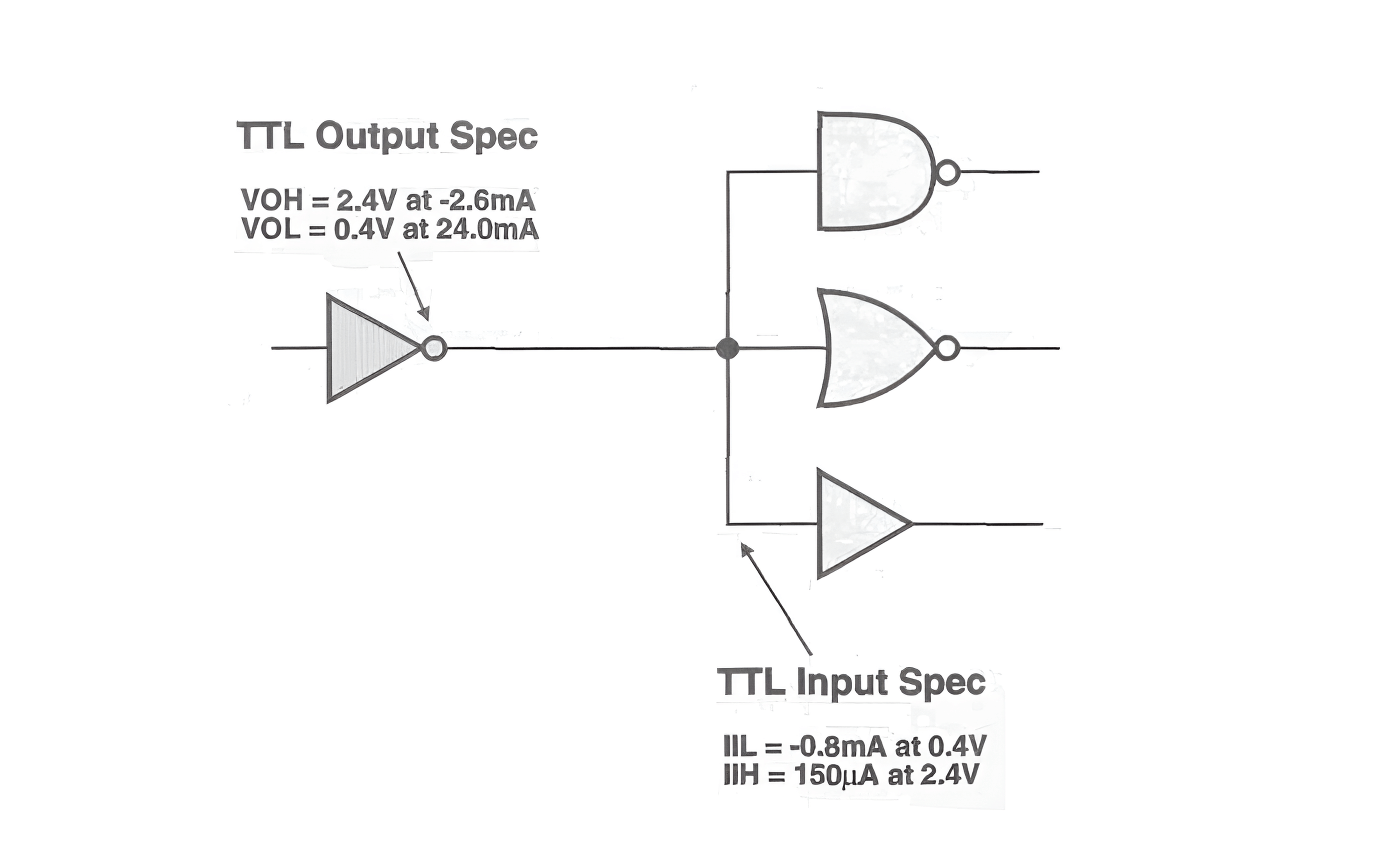

## القدرة على التفريع الناتج (Output Fanout)

قدرة التفريع (Fanout) تشير إلى قدرة أطراف الإخراج على دفع عدة أطراف الإدخال بناءً على معلمات الجهد والتيار لديها. ببساطة، إن **قدرة التفريع للأطراف تعبر عن القدرة على تحمل عدد معين من الأطراف الداخلية** بالإشارة الناتجة.

على سبيل المثال، يمكن لهذا الإخراج TTL في الشكل أعلاه رفع حوالي 17 من الأطراف الداخلية أو خفض حوالي 30 من الأطراف الداخلية. يتم تقديم معلمات الأطراف في ورقة المواصفات على النحو التالي:

| المعلمة | الوصف | شروط الاختبار | الحد الأدنى | الحد الأقصى | الوحدة |

| ------- | ------------------------- | ------------------------- | ----------- | ----------- | ------ |

| VOH | جهد الإخراج العالي | VCC = 4.75V, IOH = -2.6mA | 2.4 | | V |

| VOL | جهد الإخراج المنخفض | VCC = 4.75V, IOH = 24mA | | 0.4 | V |

| IIL | تيار الحمل الداخلي الأدنى | Vin = 0.4V | -800 | | µA |

| IIH | تيار الحمل الداخلي العالي | Vin = 2.4V | | 150 | µA |

قدرة التفريع تختلف بشكل كبير بين أجهزة TTL و CMOS، حيث يكون لدى أجهزة CMOS مقاومة داخلية عالية، لذا نظريًا يمكن لإخراج CMOS دفع عدد غير محدد من الإدخالات الداخلية. ومع ذلك، تحتوي أطراف الإدخال CMOS على سعة دخيلة، وكلما زاد عدد الإدخالات المتصلة، زادت السعة. وعند تبديل الإشارة بين الأوضاع العالية والمنخفضة، سيكون هناك تأخير نتيجة لتأثير شحن وتفريغ السعة.

## المراجع والشكر

- كتاب "أسس اختبار الشرائح الرقمية الشبه موصلة" (The Fundamentals Of Digital Semiconductor Testing)

- كتاب "نظرية اختبار العالم الرقمية" (DC Test Theory)

> عنوان النص: <https://wiki-power.com/>

> يتم حماية هذا المقال بموجب اتفاقية [CC BY-NC-SA 4.0](https://creativecommons.org/licenses/by/4.0/deed.zh)، يُرجى ذكر المصدر عند إعادة النشر.

> تمت ترجمة هذه المشاركة باستخدام ChatGPT، يرجى [**تزويدنا بتعليقاتكم**](https://github.com/linyuxuanlin/Wiki_MkDocs/issues/new) إذا كانت هناك أي حذف أو إهمال.