أساسيات اختبار الشرائح النصفية - المفاهيم الأساسية

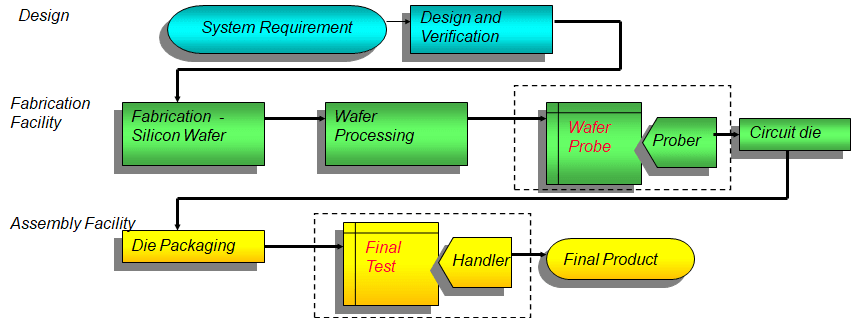

مع زيادة تكامل الشرائح، أصبح الاختبار اليدوي غير كافٍ لتلبية الاحتياجات، وبالتالي يتعين استخدام أجهزة اختبار آلية (ATE، أجهزة الاختبار الآلي). نظرًا لتعقيد الشرائح الحالية، لا يمكن للاختبار العادي على المقاعد العادية تلبية الاحتياجات. يمكن لـ ATE اكتشاف سلامة الدوائر المتكاملة وهو الخطوة النهائية في عملية تصنيع الدوائر المتكاملة لضمان جودة المنتج. يُعتبر اختبار الشرائح جزءًا من الجزء الأخير في سلسلة صناعة الشرائح النصفية. يتم تقسيم الأجهزة المختبرة إلى عدة فئات رئيسية: الذاكرة، الدوائر الرقمية، الدوائر التناظرية، والدوائر الهجينة.

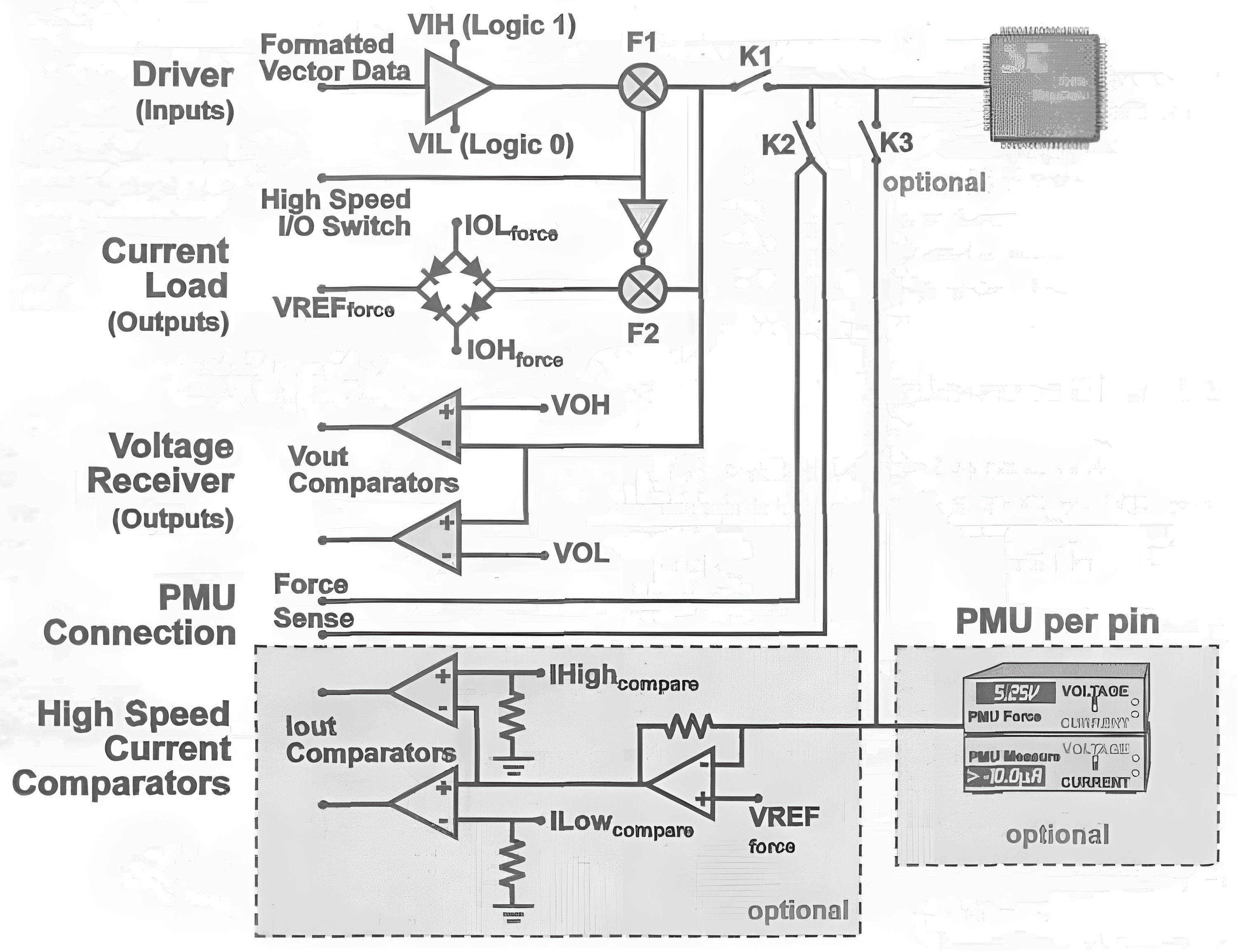

يحتوي ATE على العديد من الأنظمة الفرعية، بما في ذلك دوائر تشغيل عالية ومنخفضة الجهد، وحمل تيار قابل للبرمجة، ومقارنة جهد الإخراج، ودوائر اتصال PMU، ومقارنة تيار عالي السرعة، ومفاتيح عالية السرعة، وما إلى ذلك.

يمكن رؤية من الشكل أعلاه أن نظام الاختبار يتكون أساسًا من ثلاثة أجزاء: الإدخال والإخراج والحمل الديناميكي:

- الجزء الداخلي: يوفر جهد VIL/VIH لـ DUT.

- الجزء الخارجي: يقارن جهد الإخراج لـ DUT مع VOL/VOH.

- الحمل الديناميكي

- عن طريق تحميل تيار IOL/IOH، يتم الحصول على جهد الإخراج ومقارنته مع VOL/VOH.

- يتم مقارنة التيار المباشر للإخراج مع ILow/IHigh (عادةً متوفر في أجهزة الجودة العالية).

أساسيات الاختبار هي اختبار المعلمات التيار المستمر والمعلمات التيار المتردد. يمكن استخدام طرق القياس الثابتة مثل Static باستخدام بطاقة PE ومشغل PMU، ثم قياس الجهد عند تطبيق التيار أو قياس التيار عند تطبيق الجهد؛ يمكن أيضًا استخدام طرق الوظائف مثل Current Load و Voltage Comparator مع تشغيل نمط الاختبار.

إدخال وإخراج الإشارة

كيف يتم إنشاء الإشارة وإدخالها إلى DUT:

كيف يتم قراءة الإشارة من DUT واختبارها:

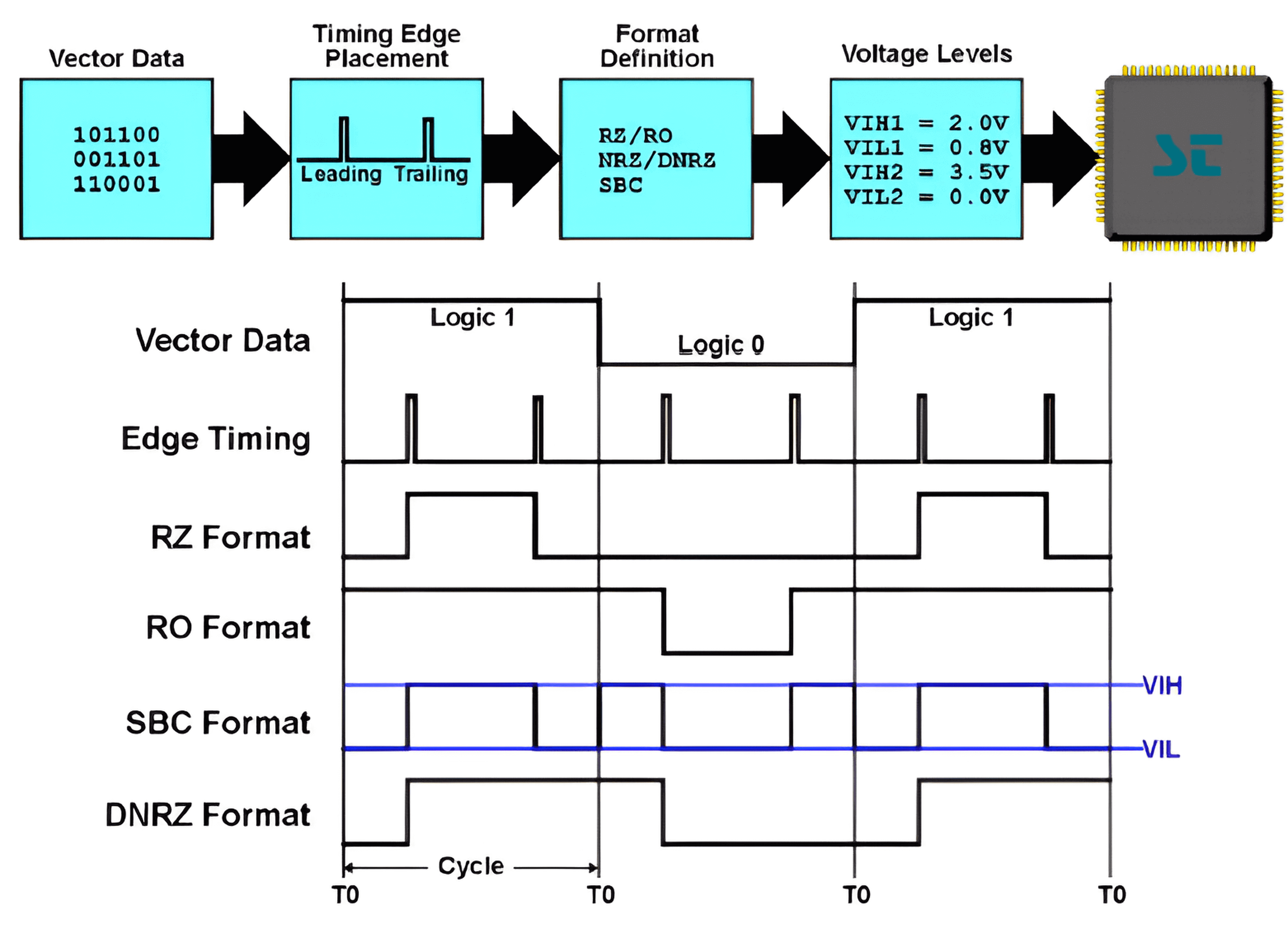

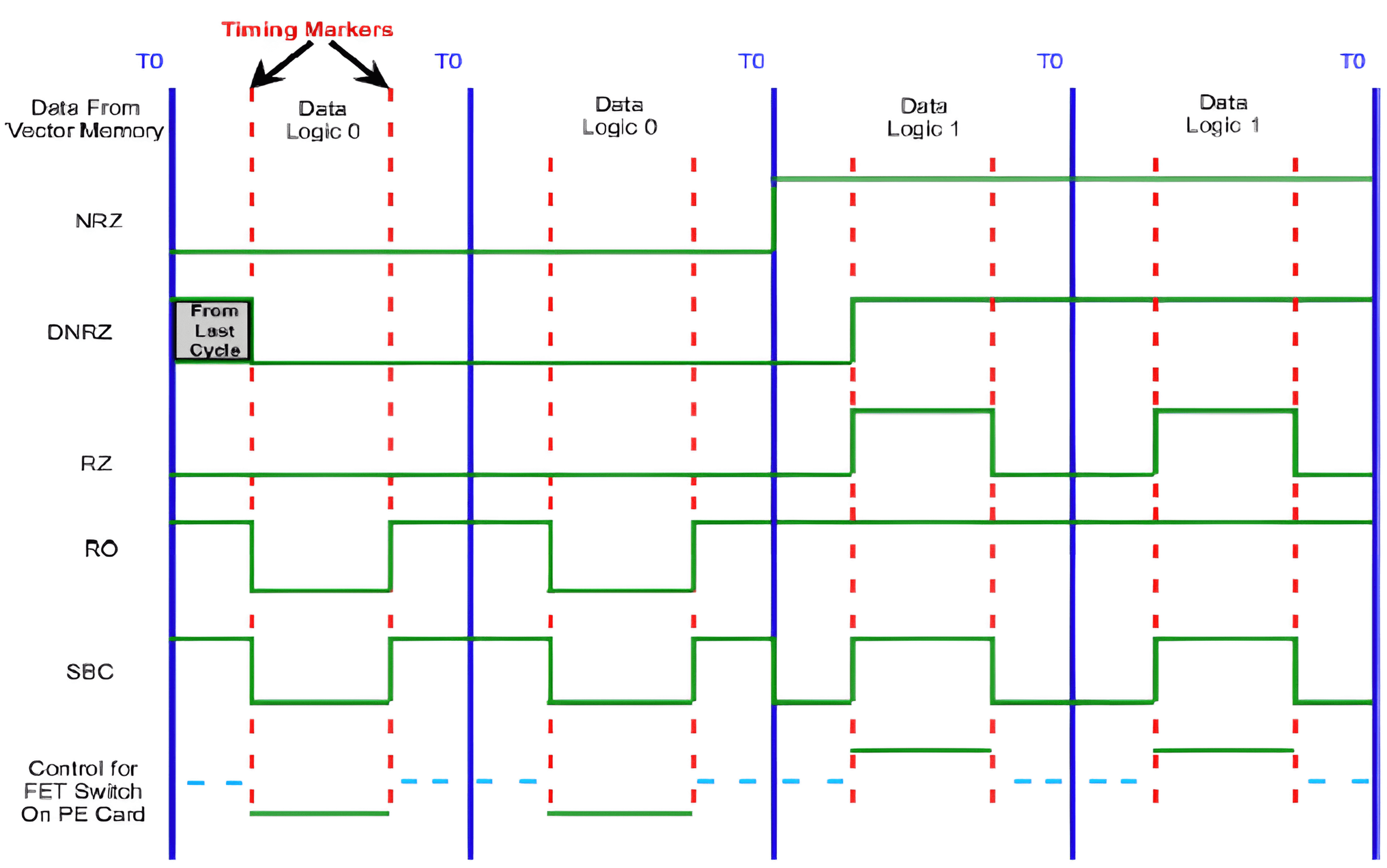

تنسيق إشارة الإدخال

- RZ (Return to Zero): رمز العودة إلى الصفر، يتم نقل بيانات البت الثنائية خلال دورة واحدة، وبعد انتهاء نبضة البت، يجب الاحتفاظ بمستوى منخفض. يمكن لهذا الترميز نقل إشارة الساعة وإشارة البيانات في نفس الوقت، ولكن بسبب استخدام جزء من النطاق الترددي للعودة إلى الصفر، فإن كفاءة النقل منخفضة نسبيًا. يمكن التحكم في مواقع الارتفاع والانخفاض بواسطة توقيت الحافة.

- RO (Return to One): رمز العودة إلى الواحد، يحتاج إلى الاحتفاظ بمستوى عالٍ عند الارتفاع. يمكن التحكم في مواقع الارتفاع والانخفاض بواسطة توقيت الحافة.

- NRZ (Non Return to Zero): رمز عدم العودة إلى الصفر يختلف عن RZ في أنه لا يحتاج إلى العودة إلى الصفر، لذا يمكن استخدام الدورة بأكملها لنقل البيانات بنسبة استخدام النطاق الترددي 100٪. إذا كانت البيانات غير متزامنة بسرعة منخفضة، فيمكن عدم استخدام خط الساعة، ولكن يجب تحديد معدل البت للاتصال (مثل UART)؛ إذا كانت البيانات متزامنة بسرعة عالية، فيجب استخدام خط ساعة إضافي. NRZ لا يتأثر بتوقيت الحافة.

- DNRZ (Delayed Non Return to Zero): رمز عدم العودة إلى الصفر المؤجل هو موجة NRZ مع تأخير زمني. يتم التحكم في الوقت المؤجل بواسطة توقيت الحافة.

- SBC (Surrounded By Complement): تعتبر مجموعة الشفرة المحيطة بالمكمل مجموعة من RZ و RO. يمكن أن يكون لديها ما يصل إلى 3 حواف في كل دورة، حيث يتم عكس البيانات في T0 وبعد فترة زمنية محددة، يتم عرض القيمة المحددة، ثم يتم عكسها مرة أخرى بعد فترة زمنية محددة. يستخدم SBC بشكل أكثر شيوعًا لإنشاء / الحفاظ على تحكم الإشارة.

- ZD (Impedance Drive): يستخدم تشغيل المقاومة للتحكم في فتح أو إغلاق الأطراف (حالة مقاومة عالية).

عادةً ما يتم استخدام تنسيق RZ/RO لإشارة الساعة، وتنسيق RZ للإشارات ذات الارتفاع الفعال (مثل تحديد الشريحة CS أو قراءة READ)؛ يتم استخدام تنسيق RO للإشارات ذات الانخفاض الفعال (مثل تمكين الإخراج OE)؛ يتم استخدام تنسيق SBC للإشارات ذات متطلبات زمن الإنشاء والاحتفاظ بالبيانات؛ يمكن استخدام تنسيق NRZ أو DNRZ للإشارات الأخرى.

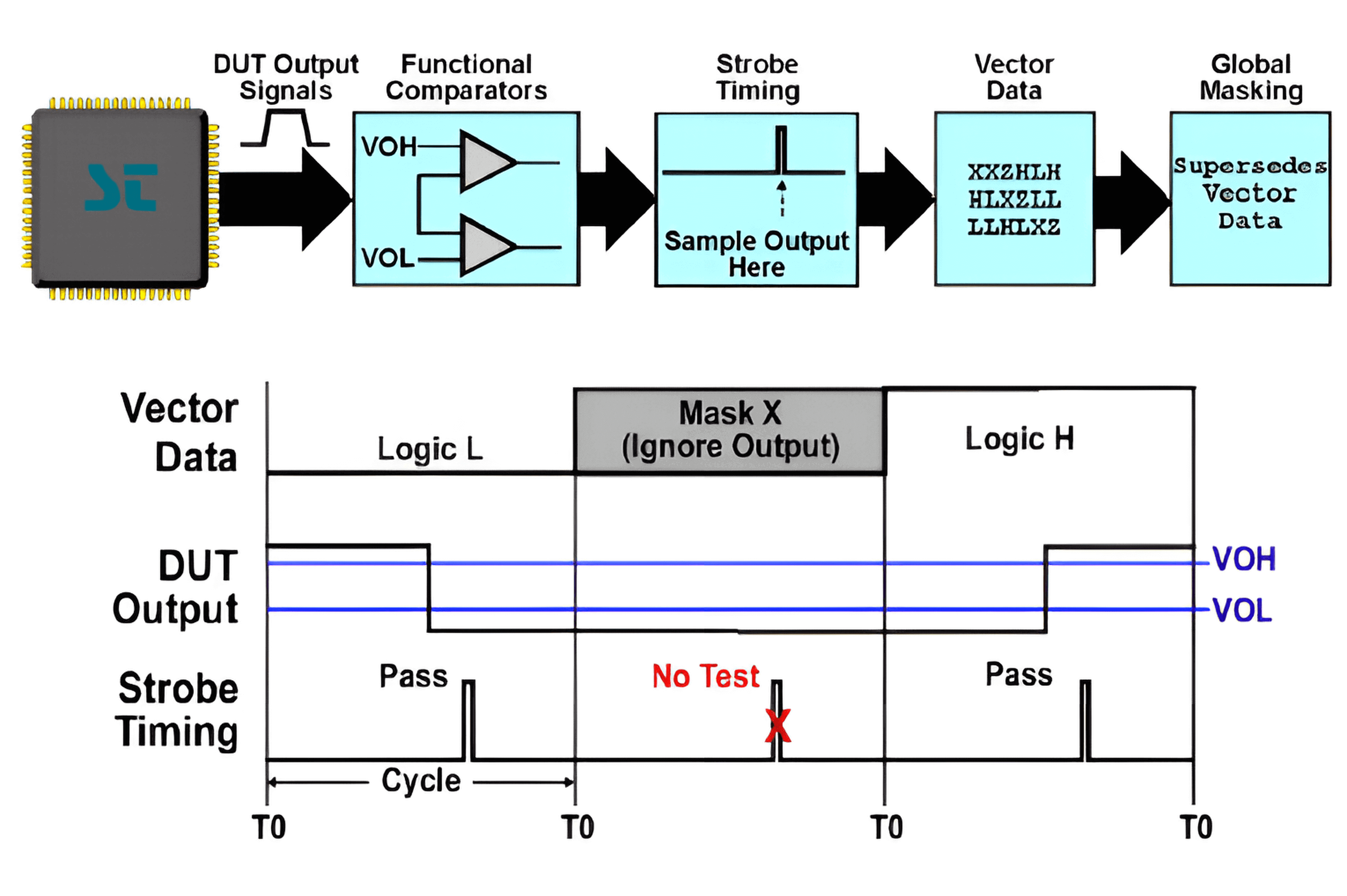

تنسيق إشارة الإخراج

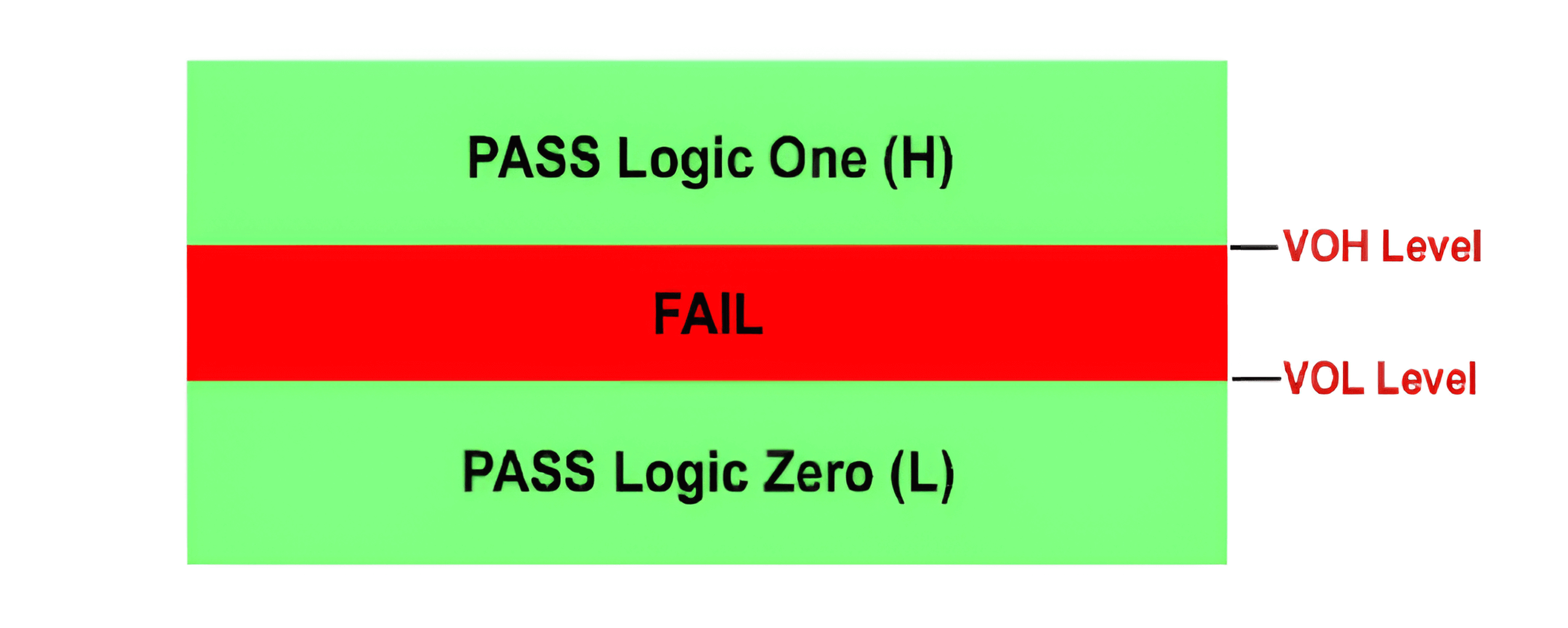

إخراج المستوى العالي والمنخفض

عند تطبيق مستوى الجهد المنخفض والمستوى العالي على الإخراج ، يجب أن يكون المستوى العالي على الأقل أعلى من VOH ، ويجب أن يكون المستوى المنخفض على الأقل أقل من VOL.

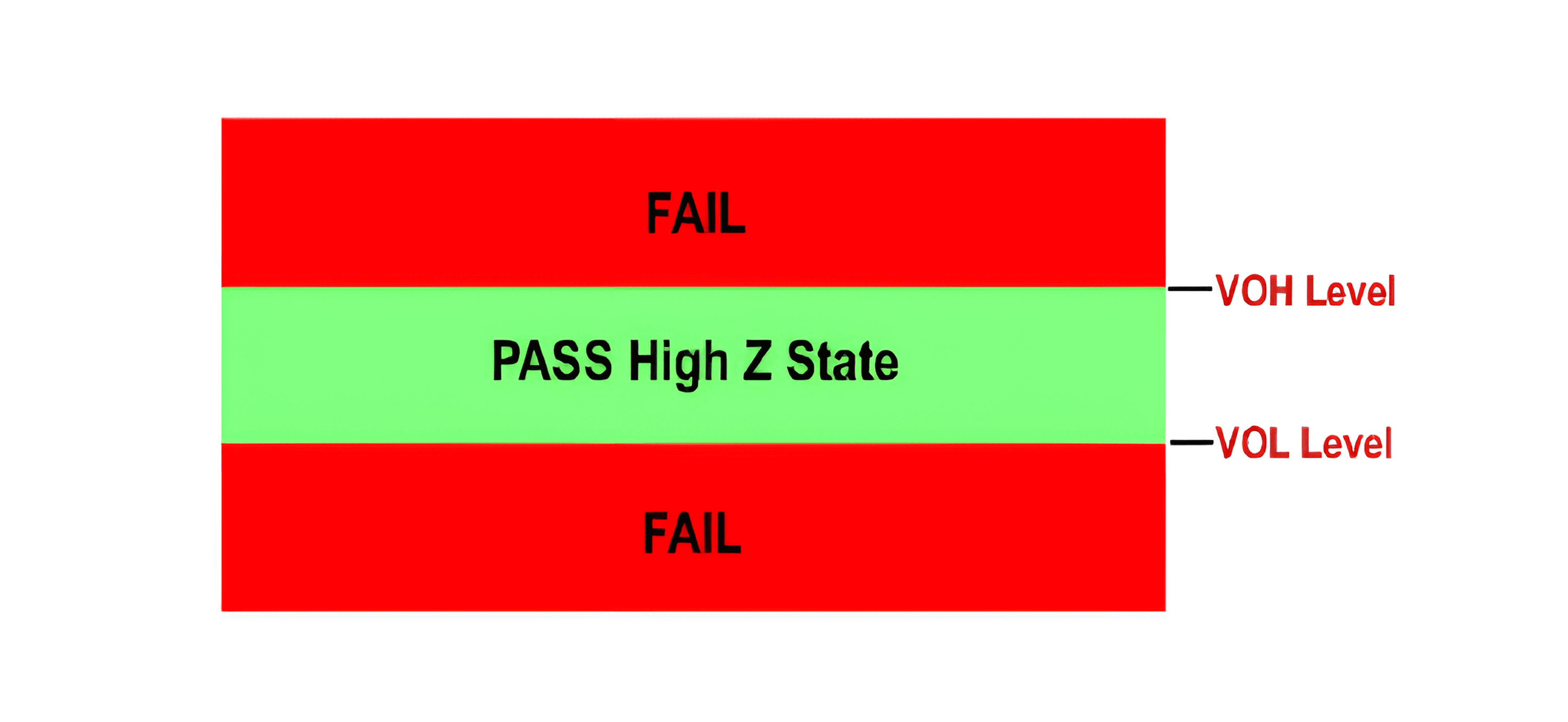

حالة الإخراج عالية المقاومة

يتم سحب جهاز الاختبار (DUT) بواسطة حمل خارجي للجهد بين VOL و VOH ، ولا يمكن أن يخرج جهد أو تيار.

إخراج تيار الحمل

يمكن لبعض أقطاب DUT إخراج تيار الحمل. إذا كان لدى نظام الاختبار حمل تيار قابل للبرمجة ، فيمكن اختباره مباشرة ، وإلا فقد يكون هناك حاجة إلى اختبار مقاومة خارجية. يتطلب إخراج تيار الحمل إخراج تيار IOL/IOH المحدد في حالة تحقيق VOL/VOH المطلوب.

تفسير المصطلحات الشائعة

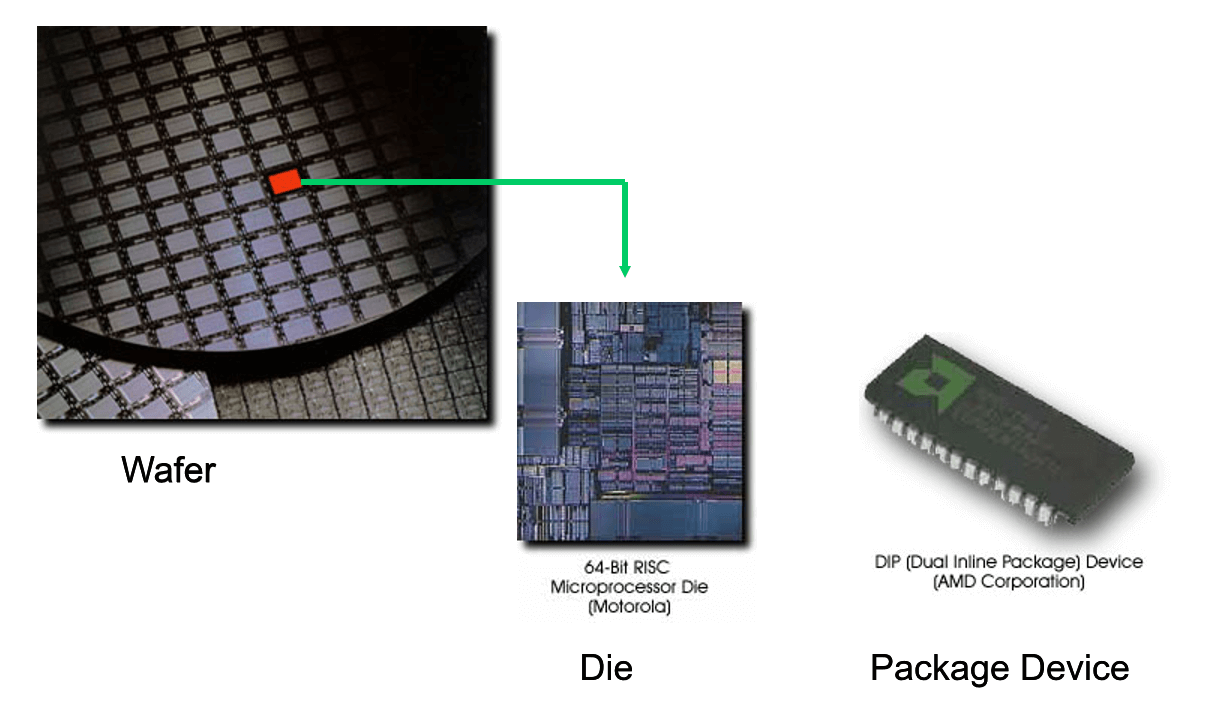

الوافر والرقاقة والتعبئة

عملية تصميم وتصنيع الشرائح:

العلاقة بين الوافر (Wafer) والرقاقة (Die) والشريحة المعبأة بعد التعبئة (Package Device) هي كما يلي:

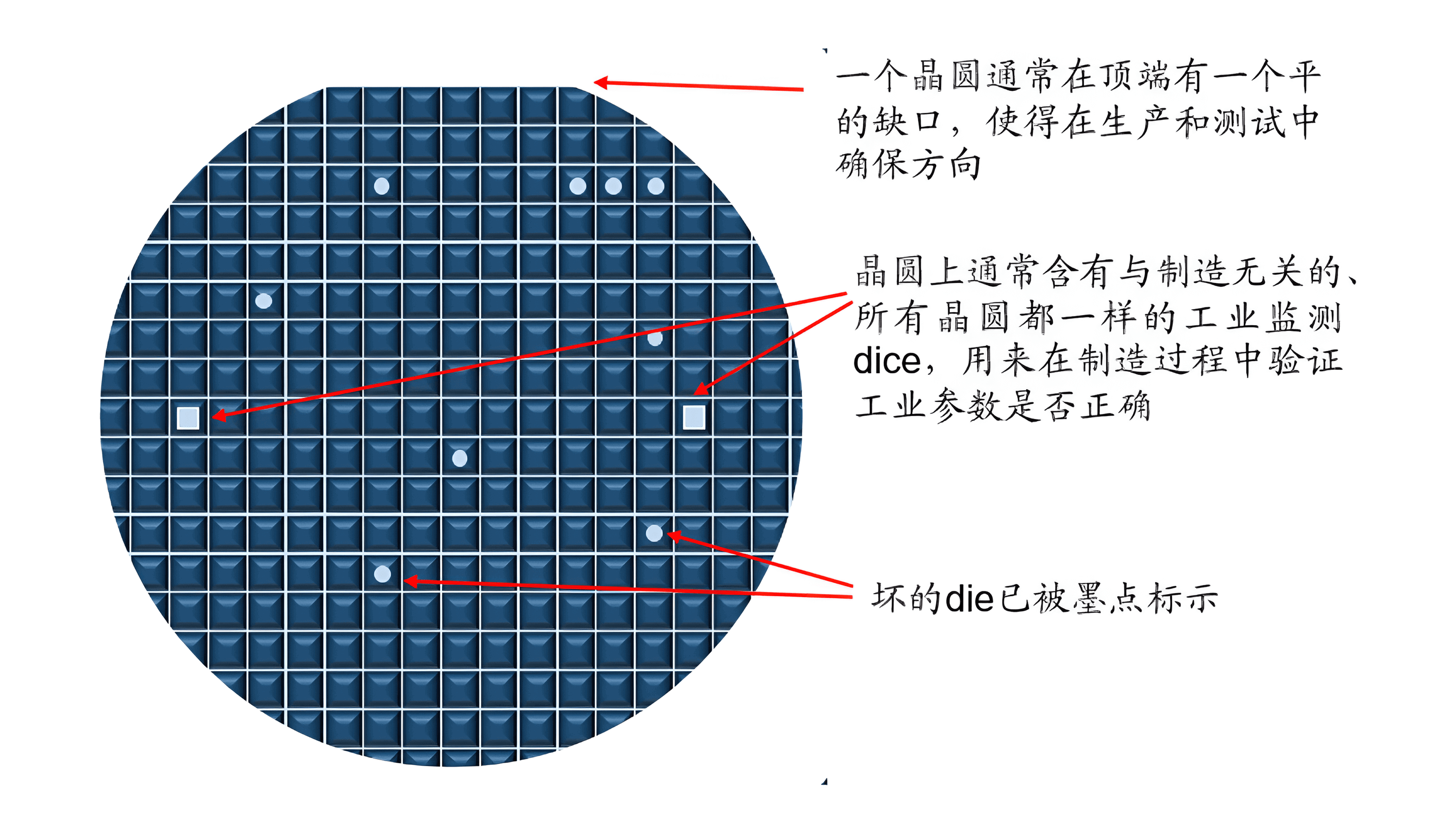

الوافر المختبر والمميز بالنقاط:

اختبار CP واختبار FT

اختبار CP (Chip Probe) هو اختبار أداء ووظائف الشريحة عندما تكون الشريحة لا تزال في مرحلة الوافر ويتم ذلك عن طريق إدخال الإبرة على أقطاب الشريحة. اختبار FT (Final Test) هو اختبار الشريحة النهائي بعد الانتهاء من التعبئة.

مصطلحات أجهزة الاختبار

- DUT (Device Under Test): الجهاز المراد اختباره ، حيث يتم اختباره من خلال أقطابه بواسطة إشارات خارجية. يُشار إليه أيضًا بـ UUT (Device Under Test).

- DPS (Device Power Supplies): أجهزة توفر الجهد والتيار المباشر لـ DUT.

- PMU (Precision Measurement Unit): وحدة قياس دقيقة تستخدم لقياس الخصائص العاصمة للأجهزة بدقة.

- PPMU (Per Pin Measurement Unit): يحتوي على وحدة PMU على كل دبوس للقياس.

- DIB (Device Interface Board): لوحة واجهة الجهاز ، وتُعرف أيضًا باسم لوحة الحمل.

- PIB (Probe Interface Board): لوحة واجهة الإبرة ، تُستخدم لاختبار الوافر.

- PDP (Prober docking plate): لوحة الواجهة بين الإبرة والمنصة.

- PROBE CARD: بطاقة PCB مع إبرة ، تُستخدم لاختبار الوافر.

- BINNING: فرز DUT وفقًا لنتائج الاختبار.

- MANIPULATOR: هيكل يدعم رأس الاختبار ويسمح له بالحركة في اتجاهات متعددة.

- HANDLER: IC pick up and place handler ، آلة تلقي وتوضيب الشرائح تلقائيًا في مقبس رأس الاختبار.

- PROBER: منصة الإبرة ، وحدة ميكانيكية تحرك الرقاقة تحت إبرة الاختبار.

المعلمات في الاختبار

- VCC: تزويد الأجهزة TTL بالطاقة.

- VDD: تزويد الأجهزة CMOS بالطاقة.

- ICC: تيار الدفع لأجهزة TTL.

- IDD: تيار الدفع لأجهزة CMOS.

- VSS: مسار عودة التيار للمصدر.

- GND: مستوى الجهد المرجعي، يعادل عادة VSS في أجهزة التزويد بطاقة واحدة.

- IDD: التيار المستهلك من جهاز CMOS.

- ICC: التيار المستهلك من جهاز TTL.

- VIH: الحد الأدنى للجهد عند إشارة مدخل عالية المستوى (لا يتم تعريفها على أنها 0).

- VIL: الحد الأعلى للجهد عند إشارة مدخل منخفضة المستوى (لا يتم تعريفها على أنها 1).

- VOH: الحد الأدنى للجهد عند إشارة خرج عالية المستوى (لا يتم تعريفها على أنها 0).

- VOL: الحد الأعلى للجهد عند إشارة خرج منخفضة المستوى (لا يتم تعريفها على أنها 1).

- IIH: أقصى تيار يمكن تدفقه عندما يكون مدخل الدبوس منطقيًا عالي المستوى.

- IIL: أقصى تيار تسرب عندما يكون مدخل الدبوس منطقيًا منخفض المستوى.

- IOH: حجم تيار الدفع / السحب (مصدر) عندما يكون خرج الدبوس منطقيًا عالي المستوى.

- IOL: حجم تيار التسرب (مصب) عندما يكون خرج الدبوس منطقيًا منخفض المستوى.

- IOZH: أقصى تيار يمكن تدفقه عندما يكون خرج الدبوس منطقيًا عالي المستوى وفي حالة مقاومة عالية.

- IOZL: أقصى تيار يمكن تدفقه عندما يكون خرج الدبوس منطقيًا منخفض المستوى وفي حالة مقاومة عالية.

- Propagation Delay: الفاصل الزمني بين إشارة الإدخال وتغير إشارة الإخراج.

- Rise Time: الوقت اللازم للارتفاع من 10٪ إلى 90٪ من المستوى العالي للجهد.

- Fall Time: الوقت اللازم للانخفاض بالشكل المعاكس.

التبديل الساخن (Hot Switching)

التبديل الساخن أو التبديل أثناء تدفق التيار يشير إلى تبديل المرحلة عندما يكون التيار قيد التدفق (يمكن أن يكون هناك فرق في الجهد، ولكن يجب أن يكون الجهد متساوي على الجانبين). قد يؤدي ذلك إلى انخفاض عمر المرحلة أو تلفها، ويجب تجنب هذا الوضع من خلال البرمجة.

ظاهرة القفل (Latch-up)

عند تطبيق جهد مرتفع على دبوس معين، يؤدي ذلك إلى تدفق تيار كبير في أجهزة CMOS، مما يتسبب في تلف الدوائر المحلية أو حتى حرقها.

خطأ الثبات (Stuck-At Fault)

يشير خطأ الثبات (SAF) إلى حالة دبوس الإشارة التي تكون محددة عند مستوى الجهد 0/1/Z بسبب عيب في التصنيع، مما يتسبب في حدوث خطأ.

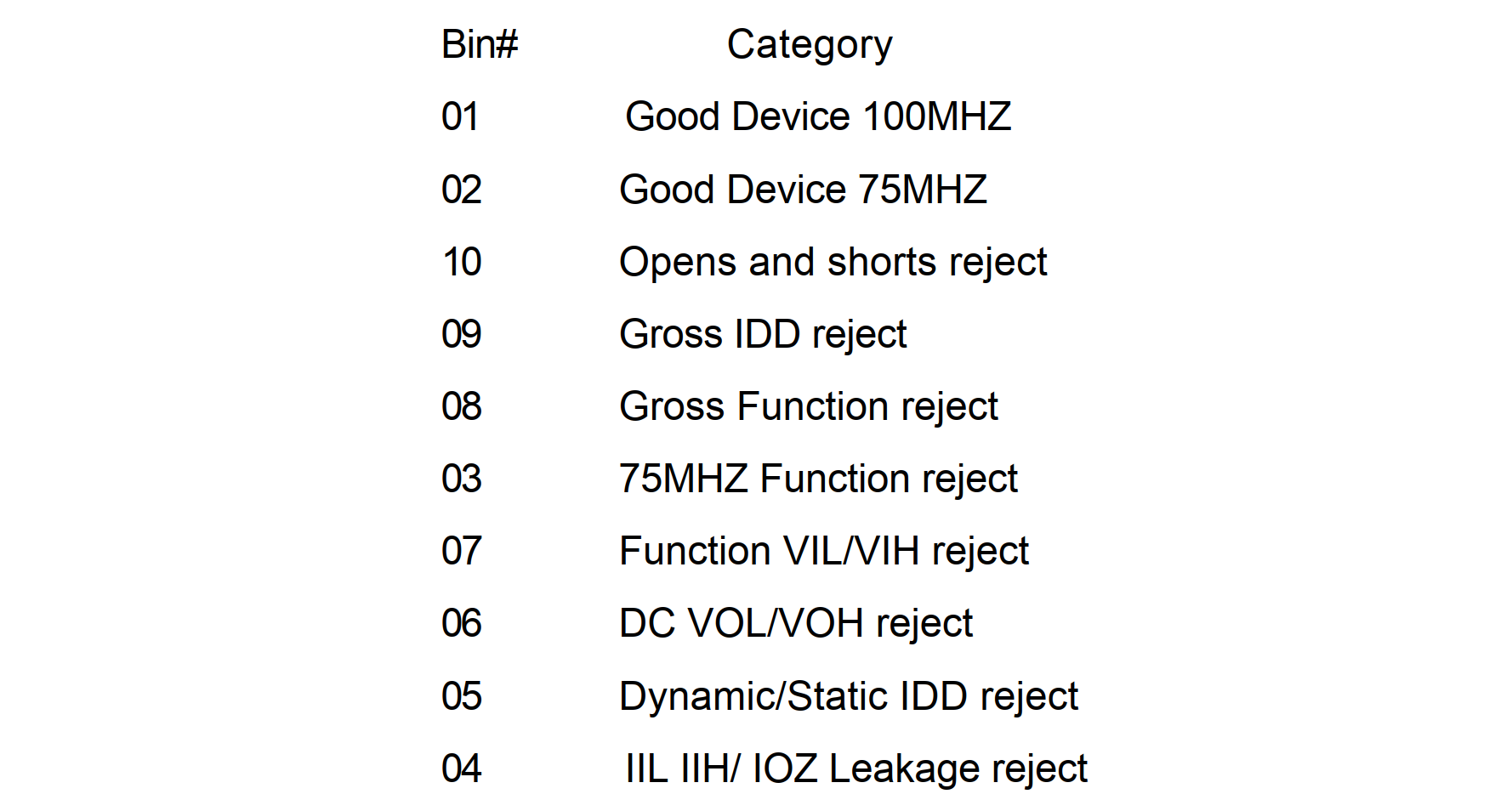

التصنيف (Binning)

التصنيف هو عملية تقسيم DUT بناءً على نتائج الاختبار. على سبيل المثال:

يشير التصنيف الصلب إلى تصنيف الأجهزة إلى مجموعتين باستخدام معدات مثل المعالج. بينما يشير التصنيف الناعم إلى تسجيل الأجهزة المعيبة في البرنامج دون تصنيفها في الواقع.

عملية التصنيف تتطلب على الأقل اثنين من الحاويات للتمييز بين نتيجة الاختبار المقبولة وغير المقبولة.

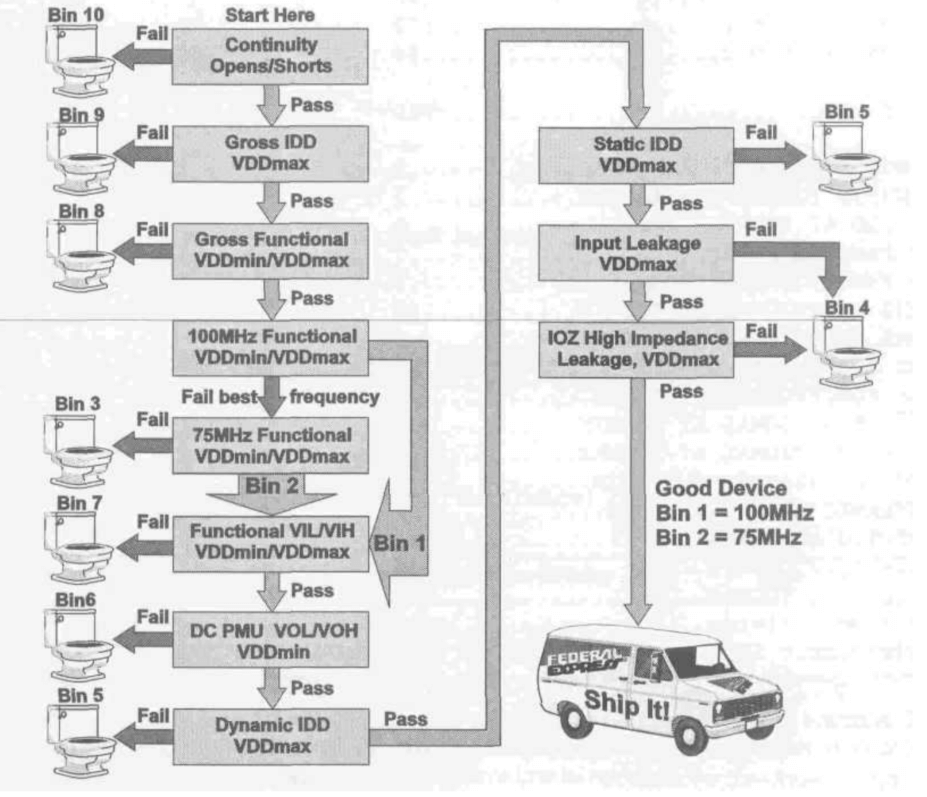

سير البرنامج (Program Flow)

تصميم سير البرنامج مهم جدًا للتجربة بأكملها. على سبيل المثال، يتطلب بعض اختبارات التيار المستمر معالجة مسبقة (تعيين منطق الجهاز المحدد مثل اختبار الوظائف)، وإذا تم إغفال هذه المرحلة، فإن نتائج الخطوات التالية ستكون بلا معنى.

يجب أن يأخذ تصميم سير البرنامج في الاعتبار العديد من العوامل مثل حجم الاختبارات والمعلمات المطلوب اختبارها وكيفية التصنيف وما إلى ذلك. عادة ما يتم تمثيلها في رسم بياني لضمان أن سير البرنامج يلبي المتطلبات.

المشاريع الأساسية للاختبار:

- اختبار الاتصال / الاستمرارية (Contact/Continuity Test): يتم فحص مشكلات الدائرة المفتوحة / القصر في أقطاب الجهاز.

- اختبار الخصائص التيار المستمر (DC PARAMETRICS TEST): يتم التحقق من معلمات التيار المستمر والجهد للجهاز، بما في ذلك IDD.

- اختبار الوظائف الرقمية (DIGITAL FUNCTIONAL TEST): يتم اختبار وظائف DUT المنطقية.

- اختبار التوقيت المتردد (AC TIMING TEST): يتم التحقق من المواصفات الترددية، بما في ذلك جودة إشارة الإخراج ومعلمات التوقيت الإشارة.

- اختبار الإشارة المختلطة (MIXED SIGNAL TEST): يتم التحقق من الدوائر التناظرية والرقمية في DUT.

- اختبارات أخرى: اختبار أجهزة الراديو الترددية (RF Devices)، وأجهزة السيارات (Automotive Devices)، وأجهزة التخزين (Memory Devices)، وأجهزة إدارة الطاقة (Power Management Devices)، وأجهزة RFID، وأجهزة الرقمية عالية السرعة (High Speed Digital devices) وغيرها.

المراجع والشكر

- "أساسيات اختبار الشرائح الإلكترونية الرقمية"

- بحث عن أجهزة اختبار الشرائح الإلكترونية: انصهار النواة والشاشة، تقاطع الضوء والكهرباء

- تفسير مفصل لظاهرة القفل (Latch-up)

- https://www.eefocus.com/ansonguo/blog?p=1

عنوان النص: https://wiki-power.com/ يتم حماية هذا المقال بموجب اتفاقية CC BY-NC-SA 4.0، يُرجى ذكر المصدر عند إعادة النشر.

تمت ترجمة هذه المشاركة باستخدام ChatGPT، يرجى تزويدنا بتعليقاتكم إذا كانت هناك أي حذف أو إهمال.