STM32F4 硬件开发

本篇文章将会对 STM32F4 的 MCU 最小系统(电源、时钟、复位、启动模式、调试管理)展开讲解。

电源

STM32F4 的正常工作电压是 1.8-3.6 V(在某些情况下可降至 1.7 V 以下,在数据手册有说明),有内置稳压器提供内部 1.2 V 的数字电源。

当主电源 VDD 断电时,可通过 VBAT 的电压为 RTC 和备份寄存器供电。

各引脚的介绍

ADC 电源和参考电压

为了提高转换精度,ADC 配有独立的电源引脚,可单独滤波并屏蔽 PCB 上的噪声。

ADC 电压源从单独的 VDDA 引脚输入。在电路设计时,应该把 VSSA 接到同个供电地,而非 VSS。

如果芯片的封装是 100 引脚以上的,就会有 VREF+ 和 VREF- 引脚,它们的作用是给 ADC 输入外部参考电压。VREF- 要接至内部 VSSA。如果芯片引脚小于 100,那么这两个引脚没有引出,在内部接在了 VDDA 和 VSSA。

后备电池电源

如果需要在 VDD 断电后保留备份寄存器内容,可将 VBAT 连到电池或其他电源。

VBAT 也可为 RTC 供电,由复位模块中内置的掉电复位 (PDR)电路进行控制。

内置稳压器

内置稳压器在复位后始终处于使能态,有三种工作模式:

- 运行:稳压器为 1.2 V 域(内核、存储器和数字外设)提供全功率电源供应。

- 停止:稳压器为 1.2 V 域提供低功率电源供应,同时保留寄存器和 SRAM 中的内容。

- 待机:稳压器掉电。除待机电路和备份域,寄存器和 SRAM 的内容都将丢失。

电路设计

以下是电源引脚的设计方法:

- VDD

- 去耦电容:总的一个 10 μF 的陶瓷/钽电容,外加每个 VDD 引脚旁接一个 100 nF 陶瓷电容。

- VDDA

- 去耦电容:100 nF 陶瓷电容 + 1 µF 陶瓷/钽电容。

- 过滤模拟噪声:可通过磁珠接至 VDD。

- VREF+

- 去耦电容:如果启用 VREF+ 功能,则需接一个 100 nF 和一个 1 µF 的电容。

- 过滤模拟噪声:可通过 47 Ω 电阻连至 VDDA。

- VBAT:接外部电池(1.65 V-3.6 V)。如果不需要电池电源,则接至 VDD 引脚。

- VCAP1/VCAP2:各对地连接一个 2.2 µF 陶瓷电容(ESR < 2 Ω);如果只有 VCAP1,则连一个 4.7 µF 陶瓷电容(ESR < 1 Ω)。

复位与电源监控

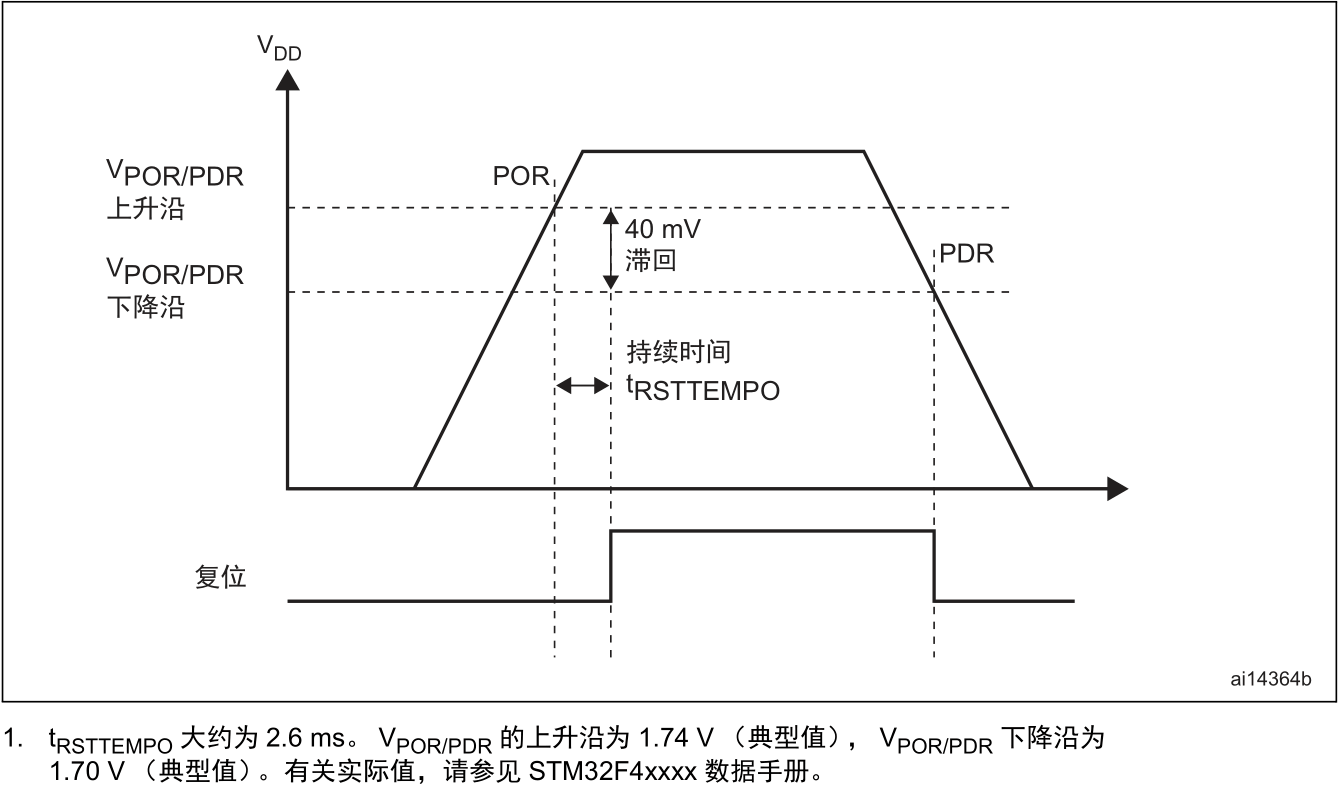

上电复位(POR)/ 掉电复位(PDR)

STM32F4 芯片中集成 POR/PDR 电路,具体上电 / 掉电复位的特征见上图。如需禁用此功能,可通过 PDR_ON 引脚实现。

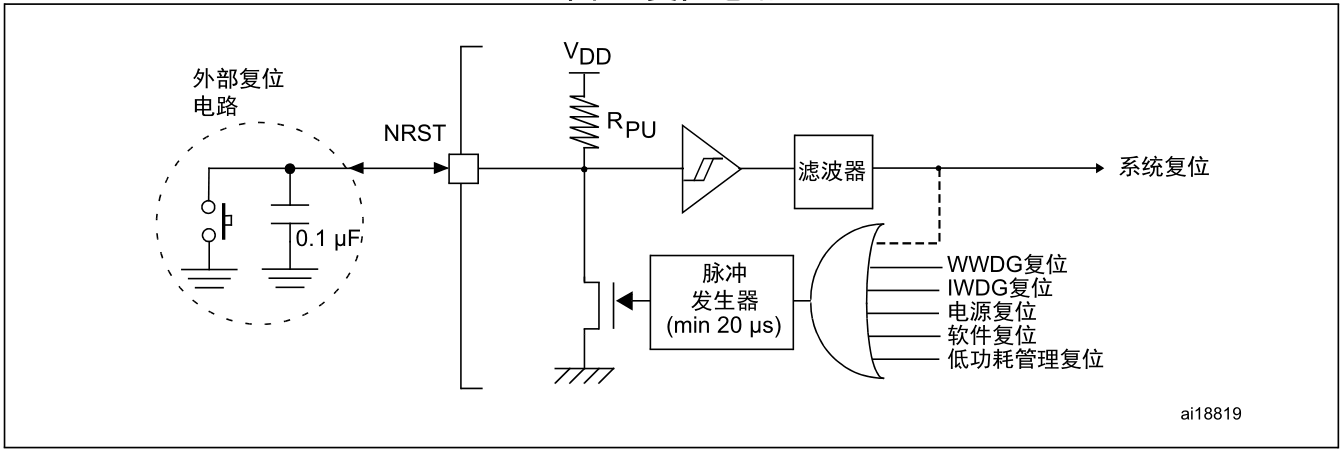

系统复位

系统复位的触发条件:

- NRST 引脚低电平(外部复位)

- 窗口看门狗计数结束(WWDG 复位)

- 独立看门狗计数结束(IWDG 复位)

- 软件复位(SW 复位)

- 低功耗管理复位

可通过查看控制 / 状态寄存器 (RCC_CSR)中的复位标志确定复位源。

即使不需要外部复位电路,也建议外加一个下拉电容以提高 EMS 性能。

时钟

在 STM32F4 上,可使用三种不同的时钟源来驱动系统时钟(SYSCLK):

- HSI(高速内部时钟信号)

- HSE(高速外部时钟信号)

- PLL 时钟

也有两种次级时钟源:

- LSI RC(32 kHz 低速内部 RC),用于驱动独立看门狗,也可用于 RTC 停机 / 待机模式下自动唤醒。

- LSE(32.768 kHz 低速外部晶振),用于驱动 RTC。

如果需要降低功耗,每个时钟在未使用时都可以单独关闭。

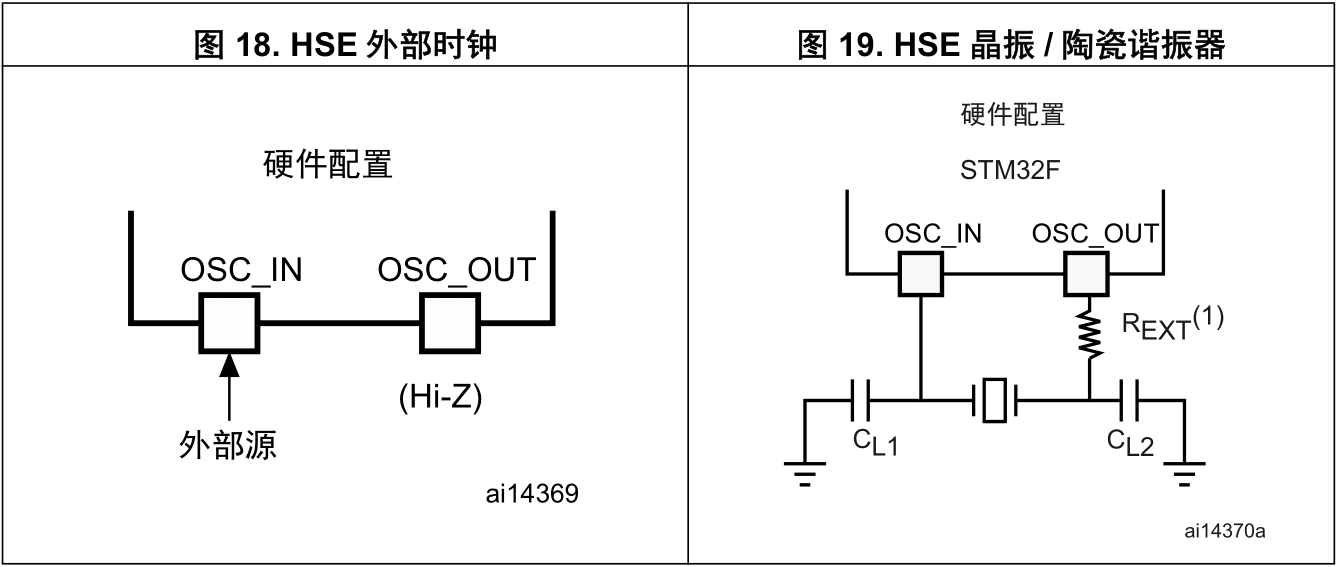

外部高速时钟(HSE)

HSE 时钟源可以有两种提供方式:外部源(有源)、外部晶振 / 陶瓷谐振器(无源)。

外部源(HSE 旁路)

如果选择有源外部时钟信号输入,则需提供 1-50 MHz 的时钟源,OSC_IN 连接占空比约为 50% 的外部时钟信号(方波、正弦波或三角波),OSC_OUT 保持高阻态。

外部晶振 / 陶瓷谐振器(HSE 晶振)

如果选用外部晶振,那么频率范围为 4-26 MHz。设计电路时,谐振器和负载电容必须尽可能地靠近振荡器的引脚,以尽量减小输出失真和起振稳定时间。负载电容值必须根据所选振荡器的不同做适当调整。

CL1 和 CL2 应选用大小相同(5-25 pF,典型值 25 pF)的陶瓷电容。

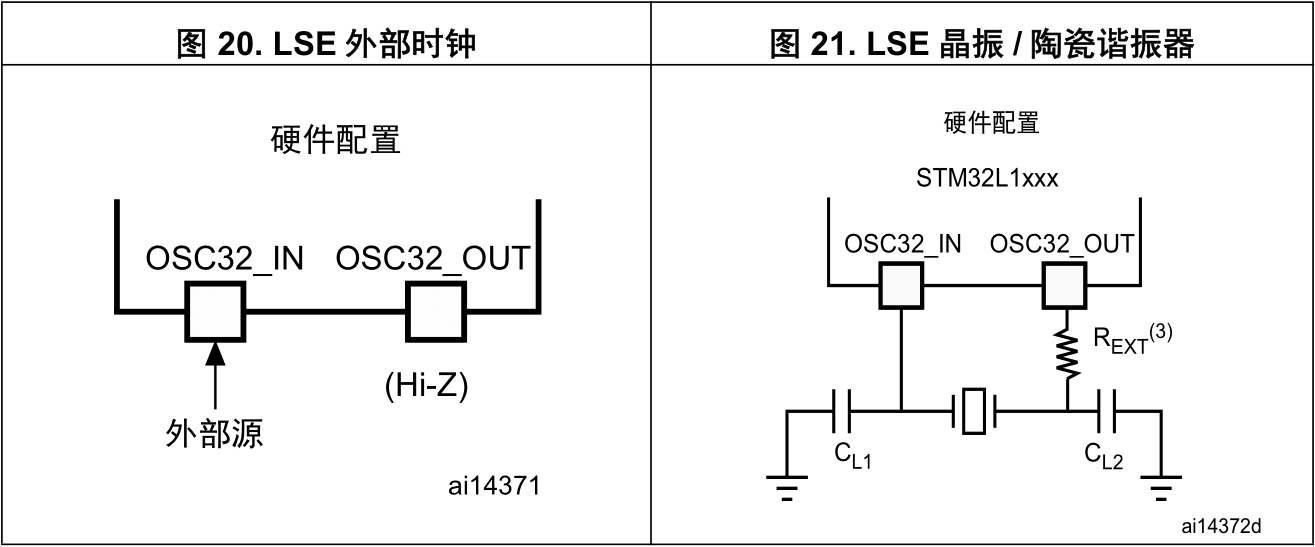

外部低速时钟(LSE)

LSE 时钟源可以有两种提供方式:外部源(有源)、外部晶振 / 陶瓷谐振器(无源)。

外部源 (LSE 旁路)

如果选择有源外部时钟信号输入,则需提供 1 MHz 以下的时钟源,OSC32_IN 连接占空比约为 50% 的外部时钟信号(方波、正弦波或三角波),OSC32_OUT 保持高阻态。

外部晶振 / 陶瓷谐振器(LSE 晶振)

如果选用外部晶振,那么频率范围为 32.768 kHz,可作为 RTC 的时钟源。设计电路时,谐振器和负载电容必须尽可能地靠近振荡器的引脚,以尽量减小输出失真和起振稳定时间。负载电容值必须根据所选振荡器的不同做适当调整。

启动模式

启动模式也叫自举模式。可通过 BOOT0 和 BOOT1 引脚来共同选择三种不同的启动模式:从主闪存存储器启动、从系统存储器启动、从内置 SRAM 启动。

启动模式的详细介绍请见文章 STM32 的启动模式

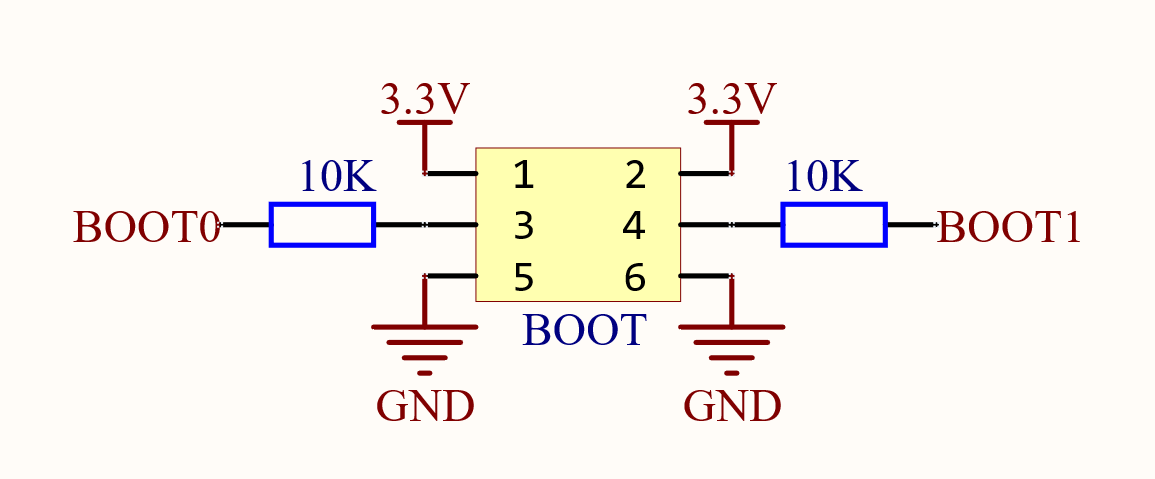

一般情况下,我们在 BOOT0 串接 10 K 的下拉电阻,BOOT1 任意即可。如果需要模式切换,那么可以参照以下的设计:

调试管理

STM32 一般使用 SWJ 协议进行下载调试。

SWJ 调试端口

STM32F4 内置 SWJ(SW/JTAG)接口。其中,SW-DP 是 2 引脚(时钟 + 数据),JTAG-DP 是 5 引脚,他们有些引脚是复用的。详细区别请见文章 SWD 与 JTAG 的区别与联系

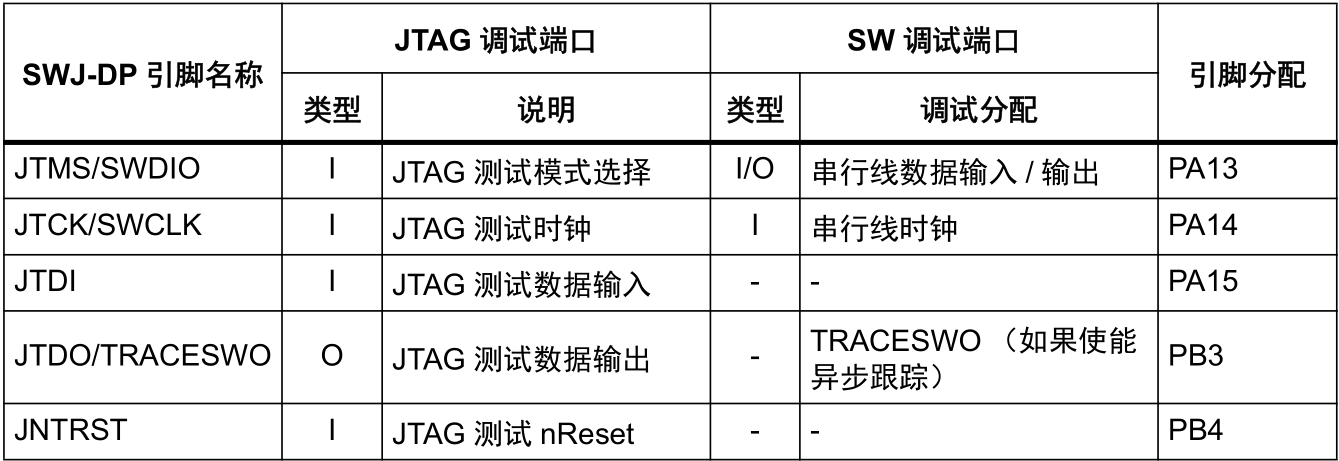

在 STM32F4 中,SWJ 的引脚分配如下:

JTAG 的内部上下拉

JTAG 引脚不能悬空(因为他们直接连着用于模式调试控制的触发器),所以在芯片内部有集成了对他们的上下拉:

- JNTRST:内部上拉

- JTDI:内部上拉

- JTMS/SWDIO:内部上拉

- TCK/SWCLK:内部下拉

软件释放 JTAG 的 I/O 后,可以作为普通的 I/O 口使用。

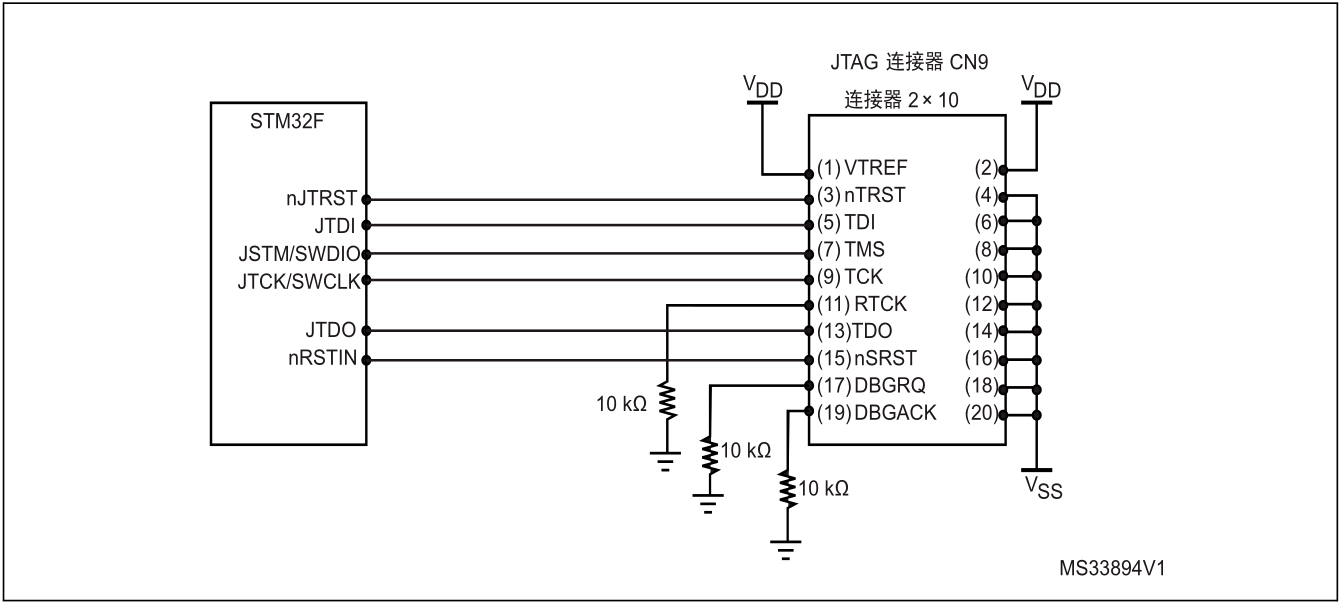

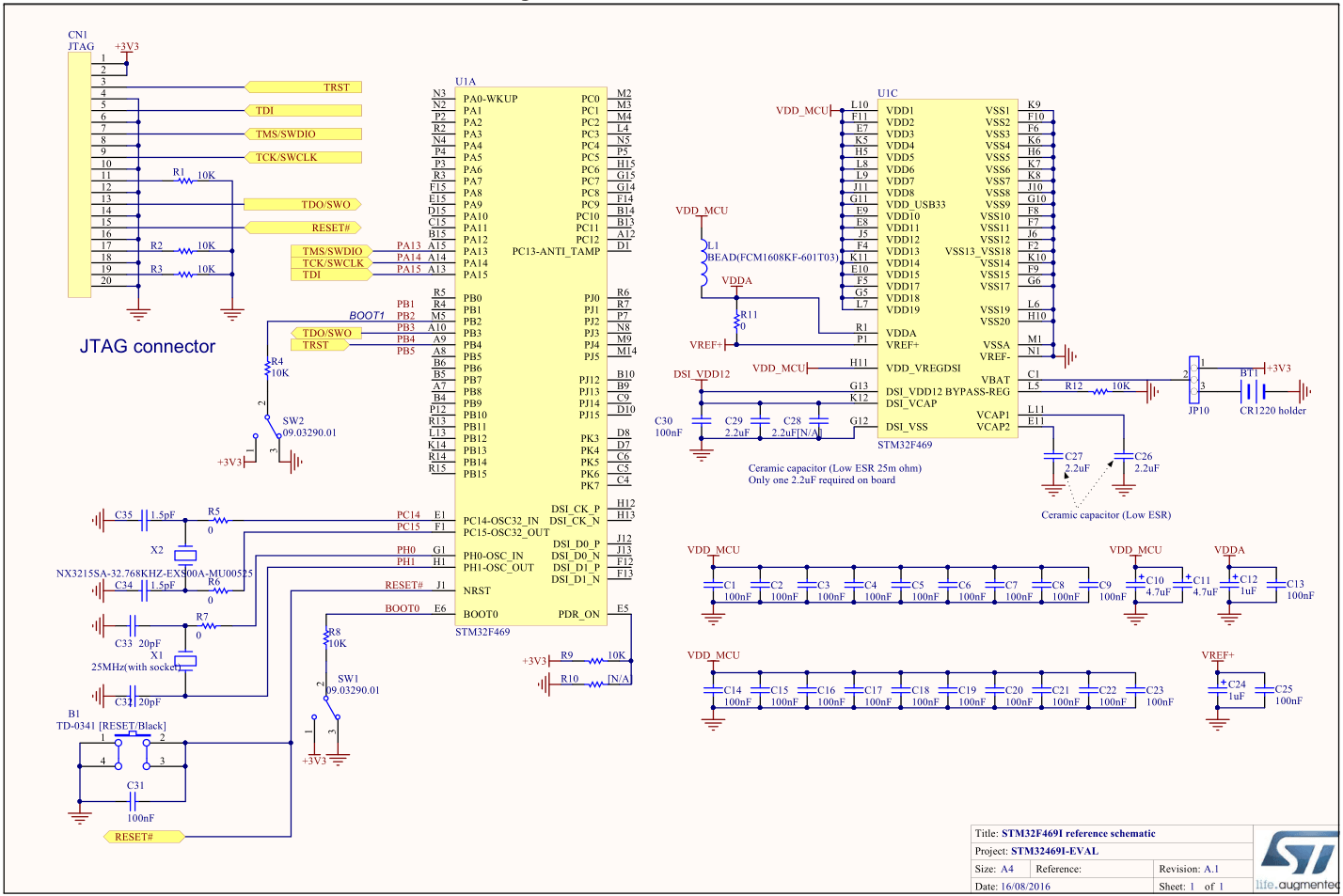

连接标准 JTAG 座的硬件设计

参考设计

参考与致谢

原文地址:https://wiki-power.com/

本篇文章受 CC BY-NC-SA 4.0 协议保护,转载请注明出处。