通信协议 - 数字逻辑电平

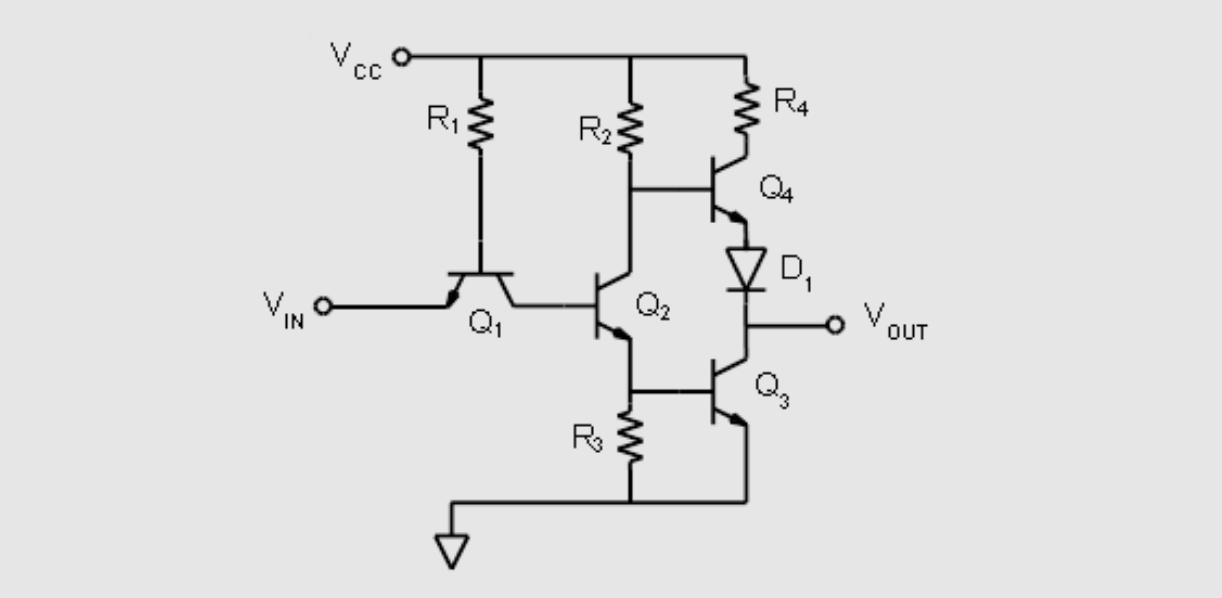

TTL 电平接口

TTL(Transistor-Transistor Logic)是基于三极管结构的,其标准电源供应为 5V。由于 2.4V 与 5V 之间还有很大空间,电压不停跳变会增加系统功耗,所以压缩形成了 LVTTL(Low Voltage Transistor-Transistor Logic)电平,分 3.3V、2.5V LVTTL。

(LV)TTL 电平的特征:

- TTL 电路通过电流控制器件,电路的速度快,传输延迟时间短(5-10ns),但是功耗大。

- TTL 电平一般过冲都会比较严重,可能在起始端串一个 22Ω/33Ω 电阻。

- TTL 电平输入脚悬空时是内部认为是高电平,如需下拉,需接 1k 以下电阻下拉。

- TTL 电平接口速度一般限制在 30MHz 以内。因为 BJT 的输入端存在几 pF 大小的输入电容(构成一个 LPF),如果输入信号超过一定频率,信号将会丢失。

- 其驱动能力一般最大为几十毫安。正常工作的信号电压一般较高,如果将它与信号电压较低的 ECL 电路接近时,会产生比较明显的串扰问题。

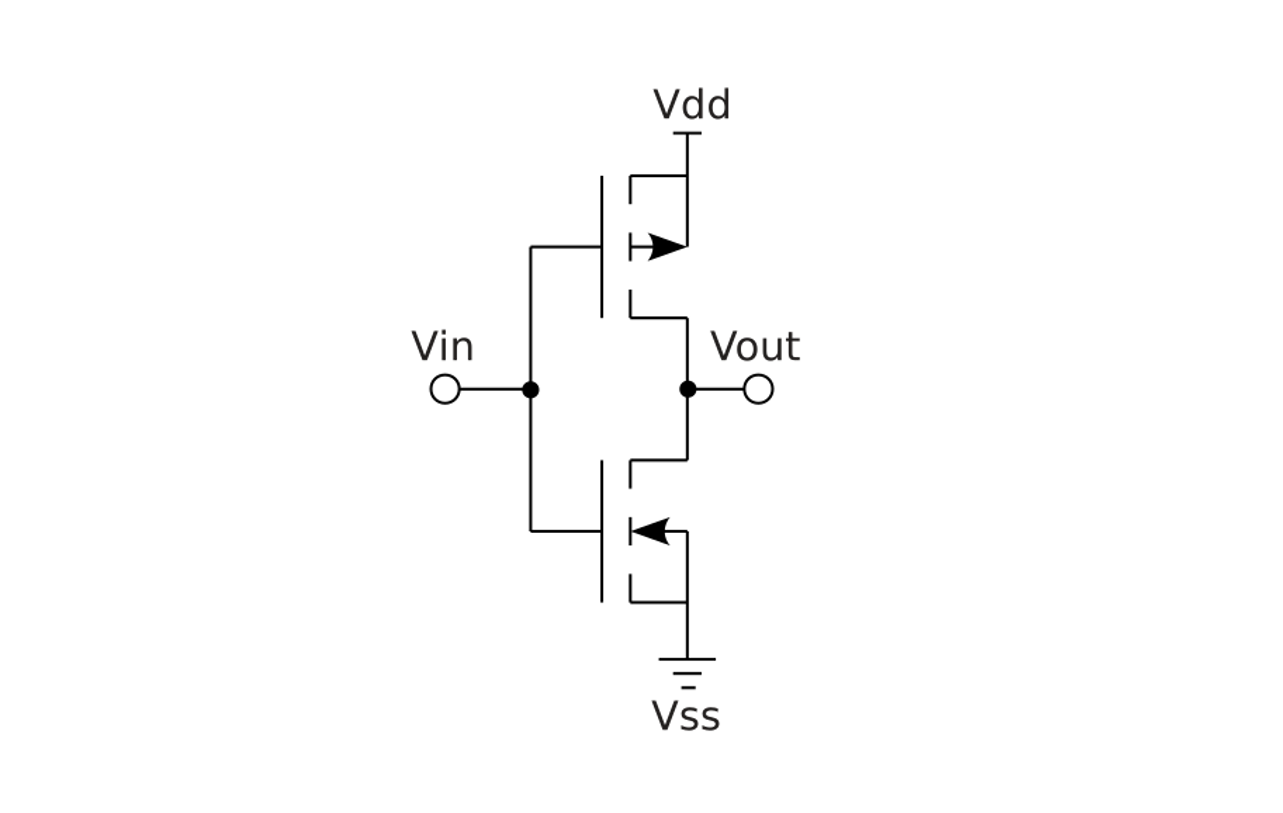

CMOS 电平接口

CMOS(Complementary Metal Oxide Semiconductor)是基于 NMOS、PMOS 组成的结构,其标准电源供应为 5V。与 TTL 同理,CMOS 也衍生出 LVCMOS 电平标准,且因 MOS 管相对于三极管的导通门电压更低,因此 LVCMOS 可比 LVTTL 使用更低的电压通信。LVCMOS 有 3.3V、2.5V、1.8V、1.5V、1.2V 标准。

(LV)CMOS 电平的特征:

- CMOS 电路通过电压控制器件,电路的速度慢,传输延迟时间长(25-50ns),但功耗低。但是在高转换频率时,CMOS 系列实际上却比 TTL 消耗更多的功率。

- CMOS 接口相对于 TTL 接口有了更大的噪声容限,输入阻抗远大于 TTL 输入阻抗。正常情况下,CMOS 的功耗和抗干扰能力远优于 TTL。

- CMOS 结构内部寄生有可控硅结构,当输入或输入管脚高于 VCC 一定值(比如一些芯片是 0.7V)时,电流足够大的话,可能引起闩锁效应,导致芯片的烧毁。

- CMOS 电路的输入阻抗是很高的,因此,它的耦合电容容量可以很小,不需要使用大的电解电容器。由于 CMOS 电路通常驱动能力较弱,所以必须先进行 TTL 转换后再驱动 ECL 电路。此外,设计 CMOS 接口电路时,要注意避免容性负载过重,否则的话会使得上升时间变慢,而且驱动器件的功耗也将增加 (因为容性负载并不耗费功率)。

各电平标准的对比

数字电路有个双阈值标准。虽然最终表示的只有 0 和 1 两个状态,但在实际电路中,电压低于多少为 0,电压高于多少为 1,是通过双阈值标准来协定的。

| \(VCC\) | \(V_{OH}\) | \(V_{IH}\) | \(V_{IL}\) | \(V_{OL}\) | \(GND\) | |

|---|---|---|---|---|---|---|

| 5V TTL | 5.0 | 2.4 | 2.0 | 0.8 | 0.4 | 0.0 |

| 3.3V LVTTL | 3.3 | 2.4 | 1.5 | 0.8 | 0.4 | 0.0 |

| 5V CMOS | 5.0 | 4.5(0.9*VCC) | 3.5(0.7*VCC) | 1.5(0.3*VCC) | 0.5(0.1*VCC) | 0.0 |

| 3.3V CMOS | 3.3 | 2.97(0.9*VCC) | 2.31(0.7*VCC) | 0.99(0.3*VCC) | 0.33(0.1*VCC) | 0.0 |

| 2.5V CMOS | 2.5 | 2.0 | 1.7 | 0.7 | 0.4 | 0.0 |

| 1.8V CMOS | 1.8 | 1.35 | 1.17 | 0.63 | 0.45 | 0.0 |

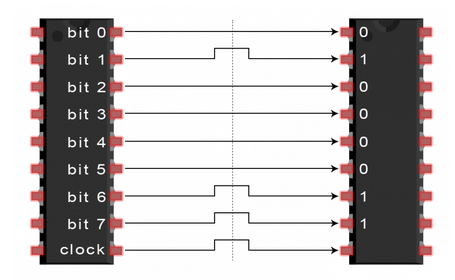

串行与并行通信

数据位可以并行或串行形式传输。在并行通信中,数据位是同时发送的,每个都通过单独的线路。下图是二进制(01000011)中字母 C 的并行传输:

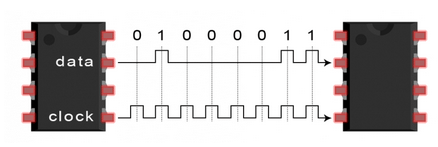

在串行通信中,通过单线逐个发送这些位。下图是字母 C 的串行传输:

参考与致谢

- 《Analog Engineer’s Pocket Reference》

- 一文了解 SPI 总线工作原理、优缺点和应用案例

- [FPGA13][电路]接口电平标准

原文地址:https://wiki-power.com/

本篇文章受 CC BY-NC-SA 4.0 协议保护,转载请注明出处。