电源方案(Buck)- LMR14050

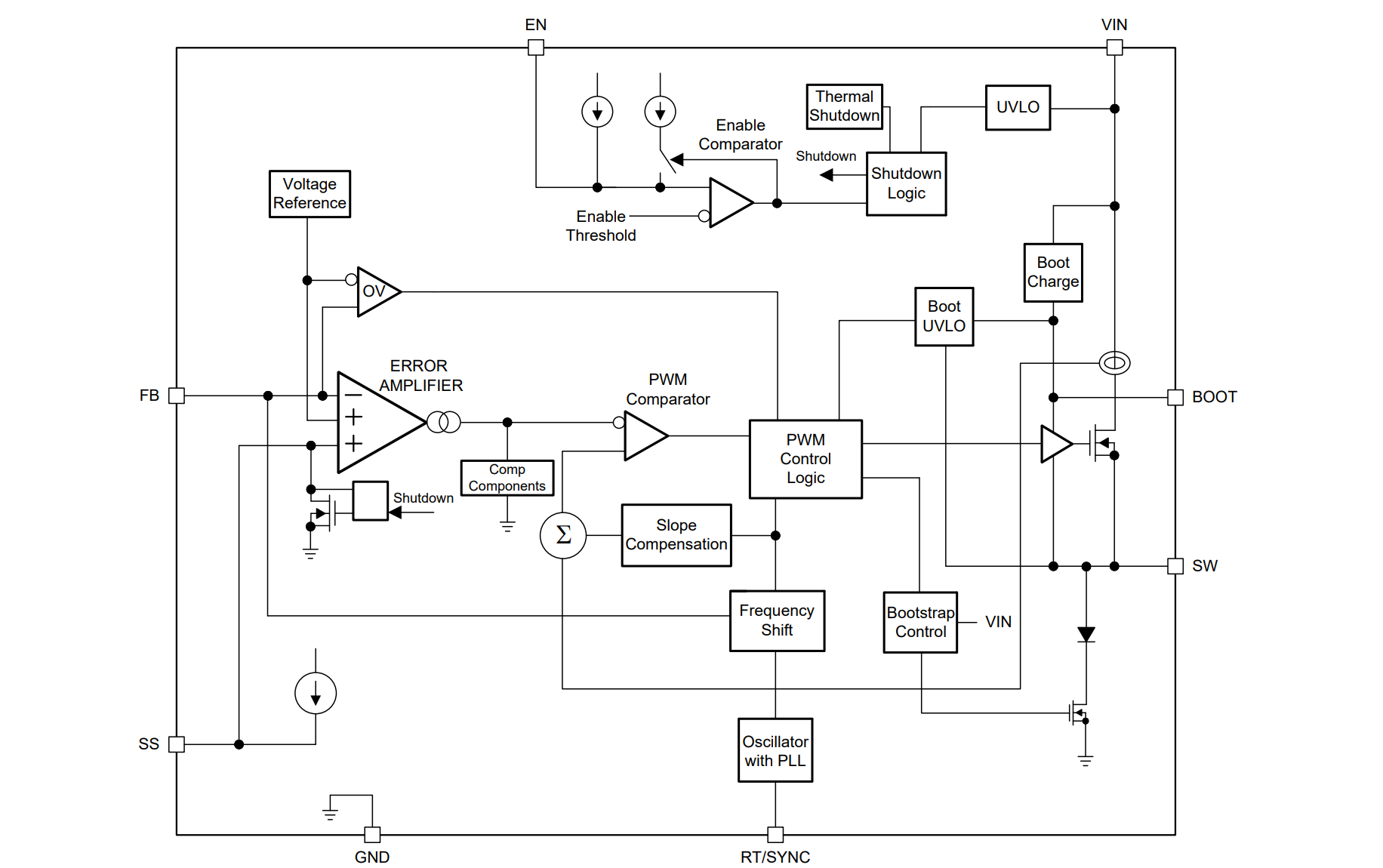

LMR14050 是 TI 的一款 Buck 转换器芯片,输入电压范围很宽(4-40V),且能提供 5A 的持续输出电流,轻载有休眠模式提高效率。它的内部集成度高,所以外围需要设计的元器件很少。开关频率能通过外部电阻 \(R_T\) 在 200kHz-2.5MHz 范围内选择,也能够与 250 kHz-2.3 MHz 频率范围内的外部时钟同步。保护功能有过温关断、\(V_{OUT}\) 过压保护(OVP)、\(V_{IN}\) 欠压锁定(UVLO)、逐周期电流限制和带频率折返的短路保护。

项目仓库: Collection_of_Power_Module_Design/DC-DC(Buck)/LMR14050

项目在线预览:

主要特性

- 拓扑:DC/DC(Buck)

- 器件型号:LMR14050SDDA

- 封装:HSOIC-8

- 输入电压:4-40 V

- 输出电压:0.8-28V

- 输出电流: 5A 持续

- 工作频率: 200kHz-2.5MHz

- 参考价格:¥ 11.3

- 其他特性

- 40µA 超低工作静态电流

- 关断电流:1µA

- 90mΩ 高侧 MOS 管

- 最短导通时间:75ns

- 电流模式控制

- 热保护、过压保护和短路保护

内部功能框图

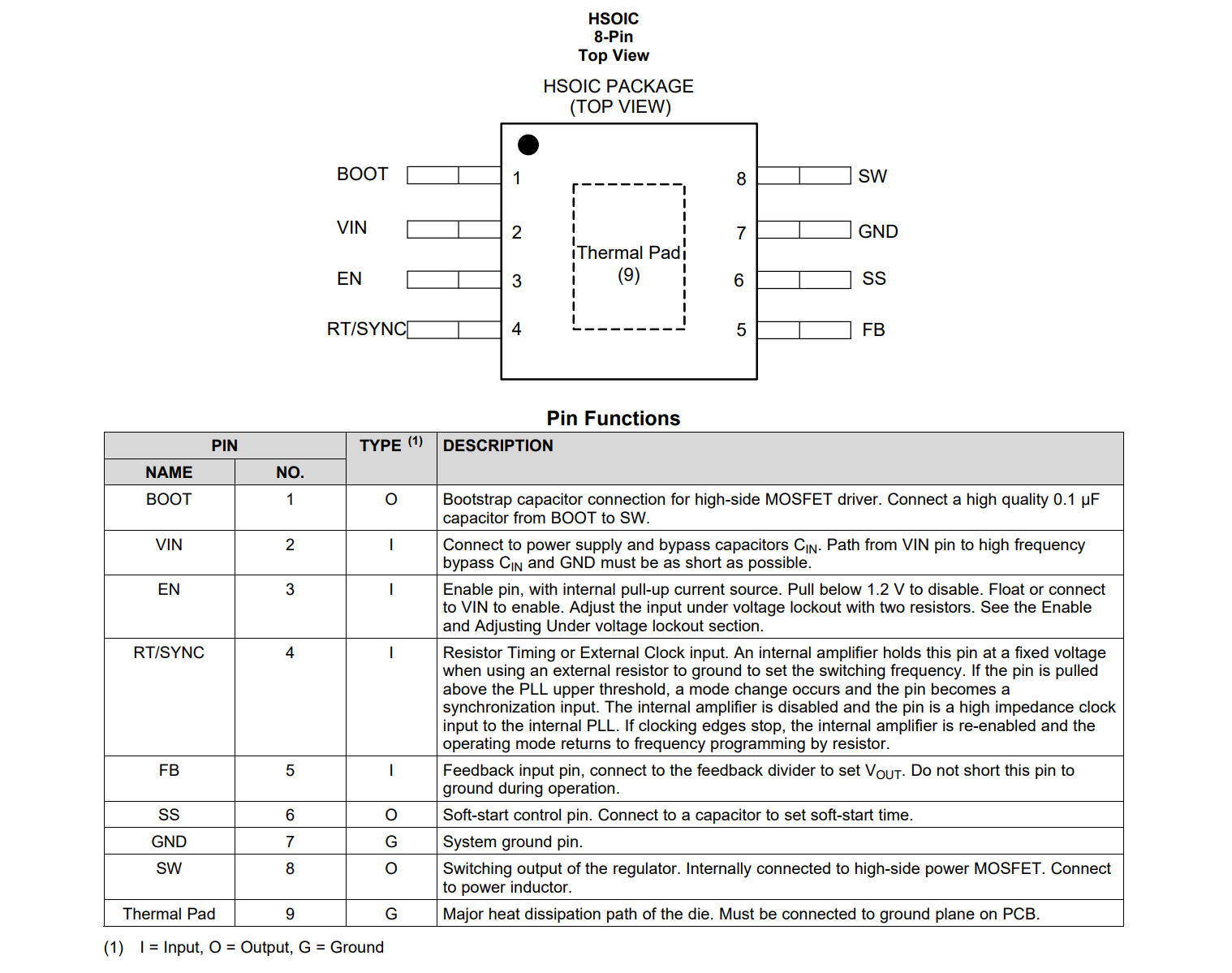

引脚定义

- BOOT:给高侧 MOS 管的自举电容。在 BOOT 和 SW 间接一个 0.1uF 电容。

- VIN:电源输入,经过去耦电容 \(C_{IN}\) 后接到此引脚。

- EN:使能开关,内部上拉。外部拉低于 1.2V 可关闭输出,浮空或接 \(V_{IN}\) 使能输出。欠压锁定的调节请见下文。

- RT/SYNC:电阻时序或外部时钟输入。当使用外部电阻接地来设置开关频率时,内部放大器将此引脚保持在固定电压。如果引脚被拉至高于 PLL 上限阈值,则会发生模式更改并且引脚变为同步输入。内部放大器被禁用,引脚是内部 PLL 的高阻抗时钟输入。如果时钟边沿停止,则重新启用内部放大器并且操作模式返回到通过电阻器进行的频率编程。?

- FB:反馈输入引脚,由电阻从 \(V_{OUT}\) 分压输入反馈,不可直接接地。

- SS:缓启动控制引脚,接电容设置缓启动时间。

- SW:稳压开关输出,在内部连高侧 MOS 管。接功率电感。

特性描述

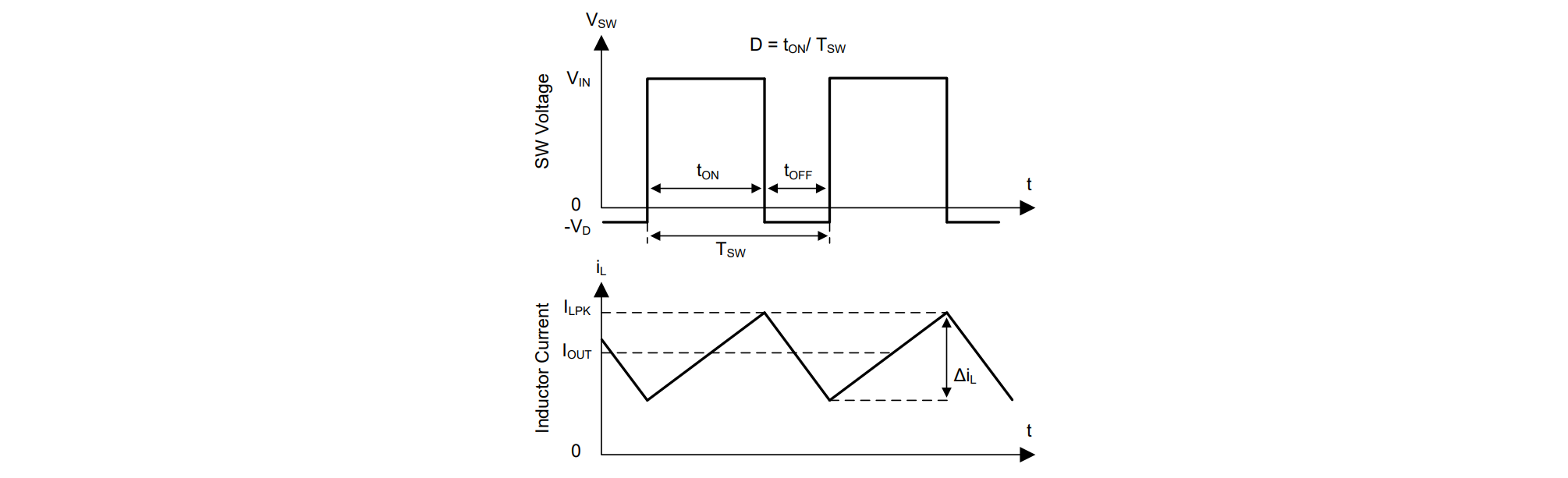

稳压原理

LMR14050 的输出电压通过开启高侧 N-MOS 并控制导通时间来调节。在高侧 N-MOS 导通期间,SW 引脚电压摆动至大约 \(V_{IN}\),电感电流 iL 随线性斜率 (\(V_{IN}\) – \(V_{OUT}\)) / L 增加;当高侧 N-MOS 关断时,电感电流通过续流二极管,以 \(V_{OUT}\) / L 的斜率放电。稳压器的控制参数由占空比 \(D = t_{ON} /T_{SW}\) 决定,其中 \(t_{ON}\) 是高端开关导通时间,TSW 是开关周期。稳压器控制环路通过调整占空比 D 来保持恒定的输出电压。在理想的降压转换器中,损耗被忽略,D 与输出电压成正比,与输入电压成反比:\(D = V_{OUT} / V_{IN}\)。

连续导通模式(CCM)下的 SW 电压与电感电流的对应关系:

睡眠模式

轻载状态下会进入睡眠模式,以提高效率、减少门极驱动损耗(通过减少开关切换)。如果输出的峰值低于 300mA 将会触发睡眠模式。

BOOT 自举电路的设计

LMR14050 内部集成了自举电压转换器,在 BOOT 和 SW 引脚接一个自举电容,就可以提供足以驱动高侧 MOS 管门极的电压。BOOT 电容的参考值为 0.1uF(X7R 或 X5R 陶瓷电容,耐压至少 16V)。

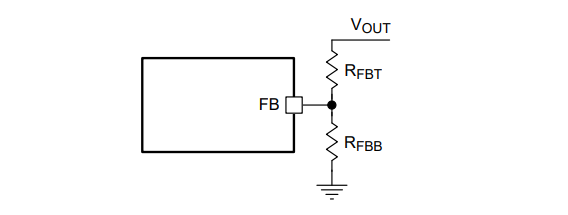

输出电压调节

LMR14050 提供一个 0.75V 的内部参考电压。输出电压通过电阻分压器,从 \(V_{OUT}\) 分压出来输入 FB 引脚,在内部进行比较调节。分压电阻建议使用偏差 1% 或更低的、温度系数 100 ppm 或更低的。通过所需分压电流选择低侧电阻 \(R_{FBB}\)(参考值是 10-100kΩ),并通过公式计算高侧电阻 \(R_{FBT}\)。选择较大的阻值有利于提高轻载效率,但如果太大,稳压器将更容易受到来自 FB 输入电流的噪声和电压误差的影响。

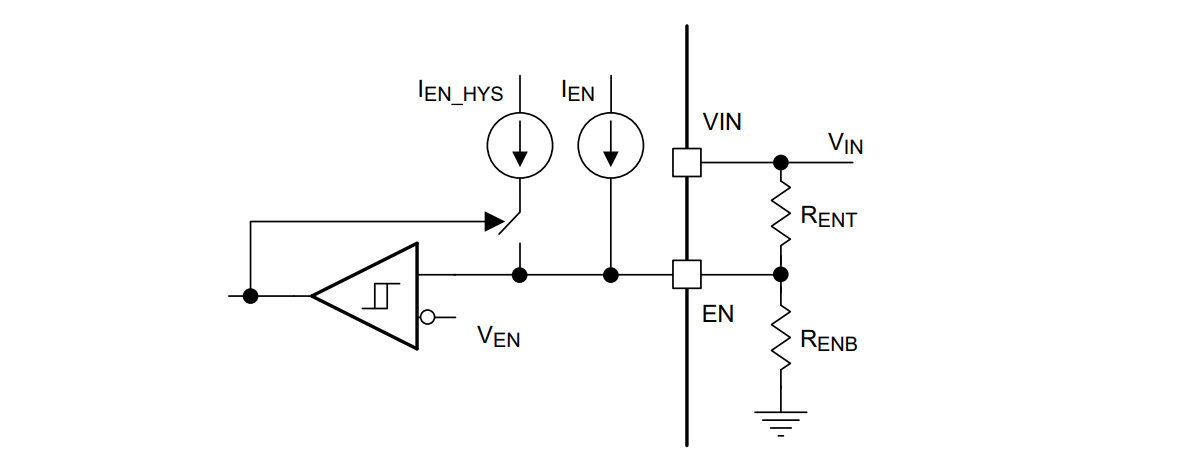

EN 使能与欠压锁定调节

当 \(V_{IN}\) 高于 3.7V,且 EN 高于 1.2V 阈值时 LMR14050 开启输出,当 \(V_{IN}\) 掉落到低于 3.52V 或 EN 低于 1.2V 时稳压器关闭。EN 有内部上拉电流源(1uA)以确保 EN 脚浮空时稳压器正常输出。

可通过调节 EN 的外部上下拉电阻,以调节启动和关闭的电压阈值:

\(R_{ENT}\) 和 \(R_{ENB}\) 遵从以下公式计算:

$$

R_{ENB}=\frac{V_{EN}}{\frac{V_{START}-V_{EN}}{R_{ENT}}+I_{EN}} $$

其中,\(V_{STRAT}\) 是希望使能启动的电压阈值,\(V_{STOP}\) 是希望欠压关闭的电压阈值,\(I_{HYS}\) 是当 EN 电压超过 1.2V 时从 EN 来的滞后电流(典型值为 3.6uA)。

外部缓启动

缓启动用于抵御通电时冲击稳压器与负载的浪涌电流,可通过外置连接于 SS 与 GND 之间的电容 \(C_{SS}\) 来进行配置。有一个内部电流源 \(I_{SS}\)(典型值为 3uA)为电容充电并生成一个从 0V 到 \(V_{REF}\) 的斜坡。缓启动时间可通过公式配置:

\(t_{SS}(ms)=\frac{C_{SS}(nF)*V_{REF}(V)}{I_{SS}(uA)}\)

在稳压器失能或内部关闭时,缓启动将会被重置。

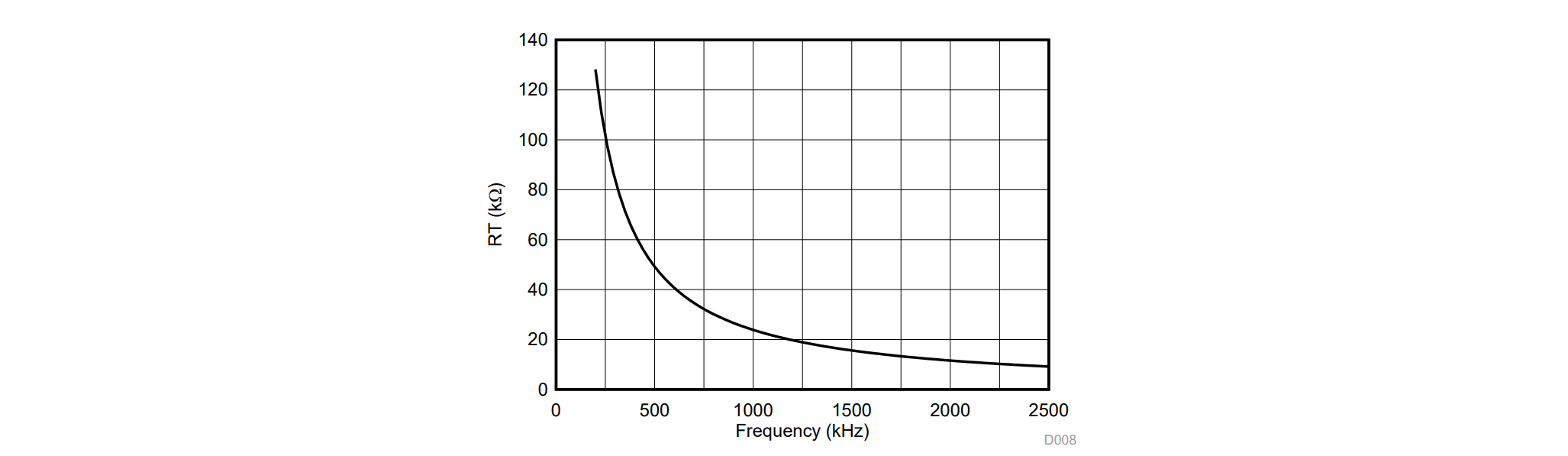

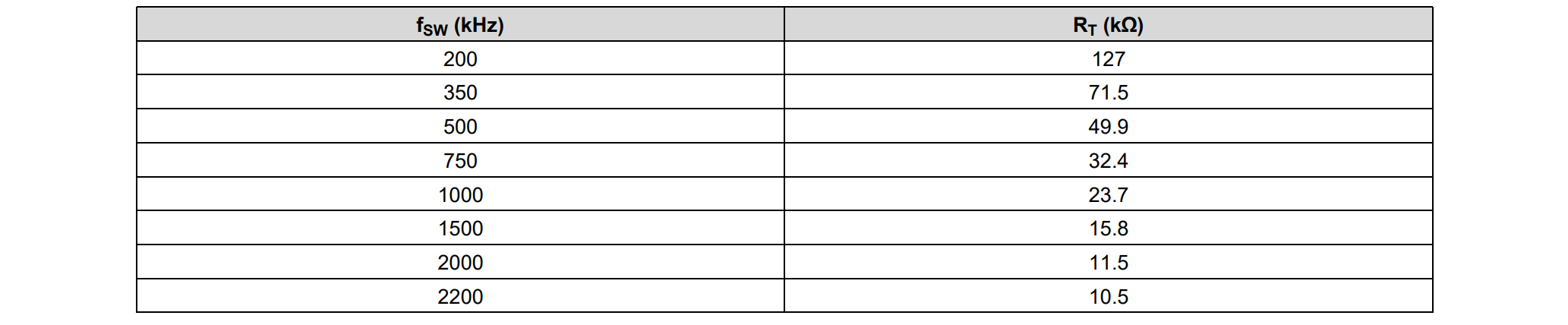

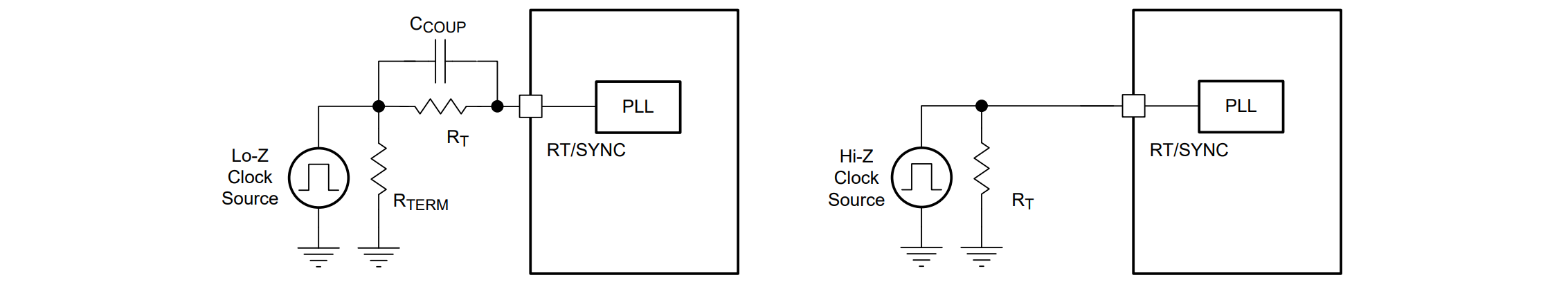

开关频率与同步(RT/SYNC)

LMR14050 的开关频率可以被接在 RT/SYNC 和 GND 之间的电阻 \(R_T\) 编程设定。RT/SYNC 引脚不可浮空或端接到地,根据以下公式或图表决定其阻值:

LMR14050 开关动作也可以被外部时钟输入信号同步(250kHz-2.3MHz):

内部晶振将会被外部时钟的下降沿同步。外部时钟推荐高电平不低于 1.7V,低电平不高于 0.5V,最小脉宽不低于 30ns。如果接低内阻信号源,那么频率设定电阻 \(R_T\) 需要被并联到 AC 耦合电阻 \(C_{COUP}\)(可为 10pF 陶瓷电容),接到终端电阻 \(R_{TERM}\)(例如 50Ω),这样可以较好地匹配阻抗。

过流与短路保护

LMR14050 通过对高侧 MOS 管的峰值电流进行逐周期电流限制,以防止过流情况。每个开关周期都会将高端开关电流与误差放大器(EA)的输出减去斜率补偿进行比较。高侧开关的峰值电流受限于恒定的钳位最大峰值电流阈值。因此,高侧开关的峰值电流限制不受斜率补偿的影响,并且在整个占空比范围内保持恒定。

过压保护

LMR14050 内置输出过压保护(OVP)电路,以最大限度减少电压过冲。当 FB 电压达到上升 OVP 阈值(VREF 的 109%)时会关闭高侧 MOS 管;当降至低于 OVP 下降阈值(VREF 的 107%)时,高侧 MOS 管恢复正常工作。

热关断保护

LMR14050 有内部热关断保护功能。当结温超过 170℃ 时热关断激活,高侧 MOS 管停止开关。当芯片温度降至 158℃ 以下,才会从内部软重启。

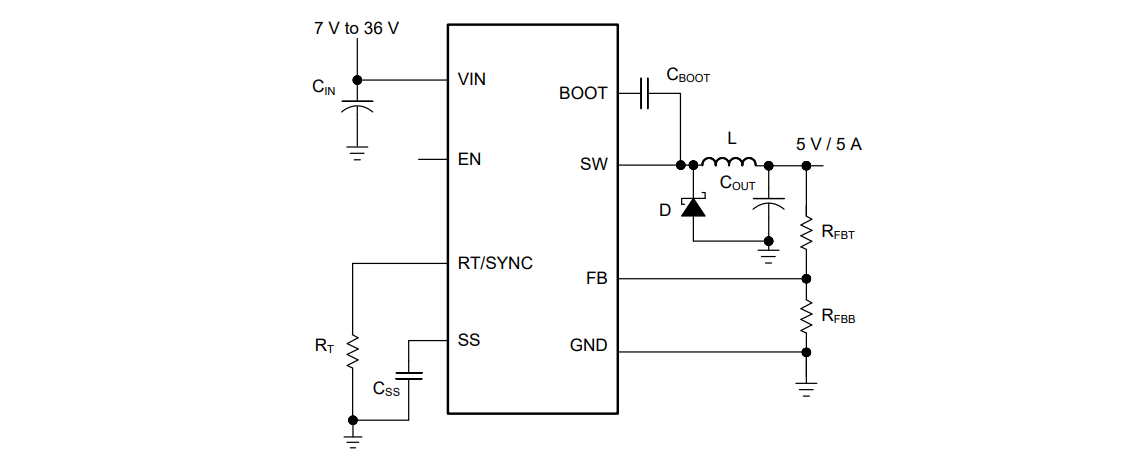

参考设计

设计参数:

- 输入电压 \(V_{IN}\):7-36V,典型值为 12V

- 输出电压 \(V_{OUT}\):5V

- 最大输出电流 \(I_{O\_MAX}\):5A

- 瞬态响应(0.5-5A):5%

- 输出电压纹波:50mV

- 输入电压纹波:400mV

- 开关频率 \(f_{SW}\):300kHz

- 缓启动时间:5ms

输出电压设置

根据上面的公式,如果我们需要输出电压为 5V,则可选 \(R_{FBT}\) 为 100kΩ,\(R_{FBB}\) 为 17.4kΩ(17.65kΩ 的近似值,经调试均衡损耗)。

如果我们需要输出电压为 12V,则可选 \(R_{FBT}\) 为 100kΩ,\(R_{FBB}\) 为 6.34kΩ(6.666kΩ 的近似值,经调试均衡损耗)。

开关频率设置

我们选择 300kHz 的开关频率,根据上面的公式,\(R_T\) 选取 84.5kΩ(83.9kΩ 的近似值)。

输出电感选型

在 DC-DC 中,电感最关键的参数是电感值、饱和电流和 RMS 电流。电感值的选取基于所需的峰-峰纹波电流 \(Δi_L\)。由于纹波电流随着输入电压的增加而增加,所以始终使用最大输入电压来计算最小电感值 \(L_{MIN}\)。输出电感的最小值可通过公式计算:

其中,\(K_{IND}\) 是表示电感器纹波电流相对于最大输出电流的系数,合理值应该是 20%-40%。在瞬时短路或过流操作事件期间,RMS 和峰值电感电流可能很高。电感电流额定值应高于电流限制。

一般来说,电感值越低越好,因为它通常带来更快的瞬态响应、更小的 DCR 及更小的尺寸。但是太低的电感值会带来较大的电感电流纹波,从而可能错误触发满载时的过流保护。由于 RMS 电流略高,它还会产生更多的传导损耗。较大的电感电流纹波,也意味着较大的输出电压纹波。对于峰值电流模式控制,不建议电感电流纹波过小,较大的峰值电流纹波可提高比较器的信噪比。

在参考设计中,\(K_{IND}\) 的值取 0.4,所以计算得到最小的电感值为 7.17uH,接近的取值为 8.2uH。可选用 7A RMS 电流和 10A 饱和电流的 8.2 μH 铁氧体电感器。

输出电容选型

输出电容 \(C_{OUT}\) 的选择直接影响稳态输出电压纹波、环路稳定性、负载电流瞬变期间的电压过冲和下冲。输出纹波本质上由两部分组成。一是电感电流纹波通过输出电容的等效串联电阻(ESR)引起的:

另一种是由电感电流纹波对输出电容充放电引起的:

这两种电压纹波并不同相,所以实际的峰-峰纹波会比两者之和小。

如果系统需要严格的电压调节(大电流阶跃和快速压摆率),则输出电容会受到瞬态性能规范的约束。当发生快速大负载提升时,输出电容能够在电感电流上升到适当水平之前,提供所需的电荷。稳压器的控制环路通常需要至少三个时钟周期,来响应输出电压下降。输出电容必须足够大,以提供三个时钟周期的电流差,以将输出电压保持在指定范围内。

当负载突然大幅下降时,输出电容会吸取电感中储存的能量。钳位二极管没法灌电流,所以电感中的电能将会导致输出电压过冲。计算特定输出下冲所需的最小输出电容的公式:

\(C_{OUT}>\frac{3*(I_{OH}-I_{OL})}{f_{SW}*V_{US}}\)

将电压过冲保持在指定范围内,所需的最小电容计算公式:

\(C_{OUT}>\frac{I_{OH}^2-I_{OL}^2}{(V_{OUT}+V_{OS})^2-V_{OUT}^2}*L\)

其中,

- \(K_{IND}\) 为电感纹波电流的纹波比(\(Δi_L/I_{OUT}\))

- \(I_{OL}\) 为负载瞬态期间的低电平输出电流

- \(I_{OH}\) 为负载瞬态期间的高电平输出电流

- \(V_{US}\) 为目标输出电压下冲

- \(V_{OS}\) 为目标输出电压过冲

在参考设计中,目标输出纹波为 50mV。假设 \(ΔV_{OUT\_ESR}=ΔV_{OUT\_C}=50mV\),\(K_{IND}\) 取值为 0.4,\(ESR\) 不大于 25mΩ,\(C_{OUT}\) 不小于 16.7 μF,参考设计的过冲和下冲范围 \(V_{US}=V_{OS}=5%*V_{OUT}=250mV\)。所以 \(C_{OUT}\) 可分别被计算出不小于 180uF 和 79.2uF,所以选取较严格的标准为 180uF,即使用 4 个 47uF(16V,X7R 陶瓷电容,ESR 为 5mΩ)并联。

肖特基二极管选型

二极管的额定击穿电压最好比最大输入电压高 25%。为了最佳可靠性,二极管的额定电流应等于稳压器最大输出电流。在输入电压远大于输出电压的情况下,二极管平均电流会更低,这时候可以使用平均电流额定值较低的二极管,约为 \((1-D) * I_{OUT}\),但峰值电流额定值应高于最大负载电流。一般选 6-7A 起步。

输入电容选型

LMR14050 需要高频输入去耦电容和大容量输入电容。高频去耦电容的典型推荐值为 4.7-10 μF(X5R/X7R,陶瓷电容,耐压为最大输入电压两倍以上)。在参考设计中,使用了两个额定电压为 100 V 的 2.2 μF X7R 陶瓷电容器。高频滤波电容需要靠近稳压器放置。

大容量电容为电压尖峰提供阻尼,参考值为 47uF 或 100uF 电解电容。

BOOT 自举电容选型

LMR14050 需要一个 BOOT 自举电容,在前文有提及,BOOT 电容的参考值为 0.1uF(X7R 或 X5R 陶瓷电容,耐压至少 16V)。

缓启动电容选型

根据前文公式,如果设定缓启动时间为 5ms,则可得出 22 nF(接近计算值 20nF)的缓启动电容。

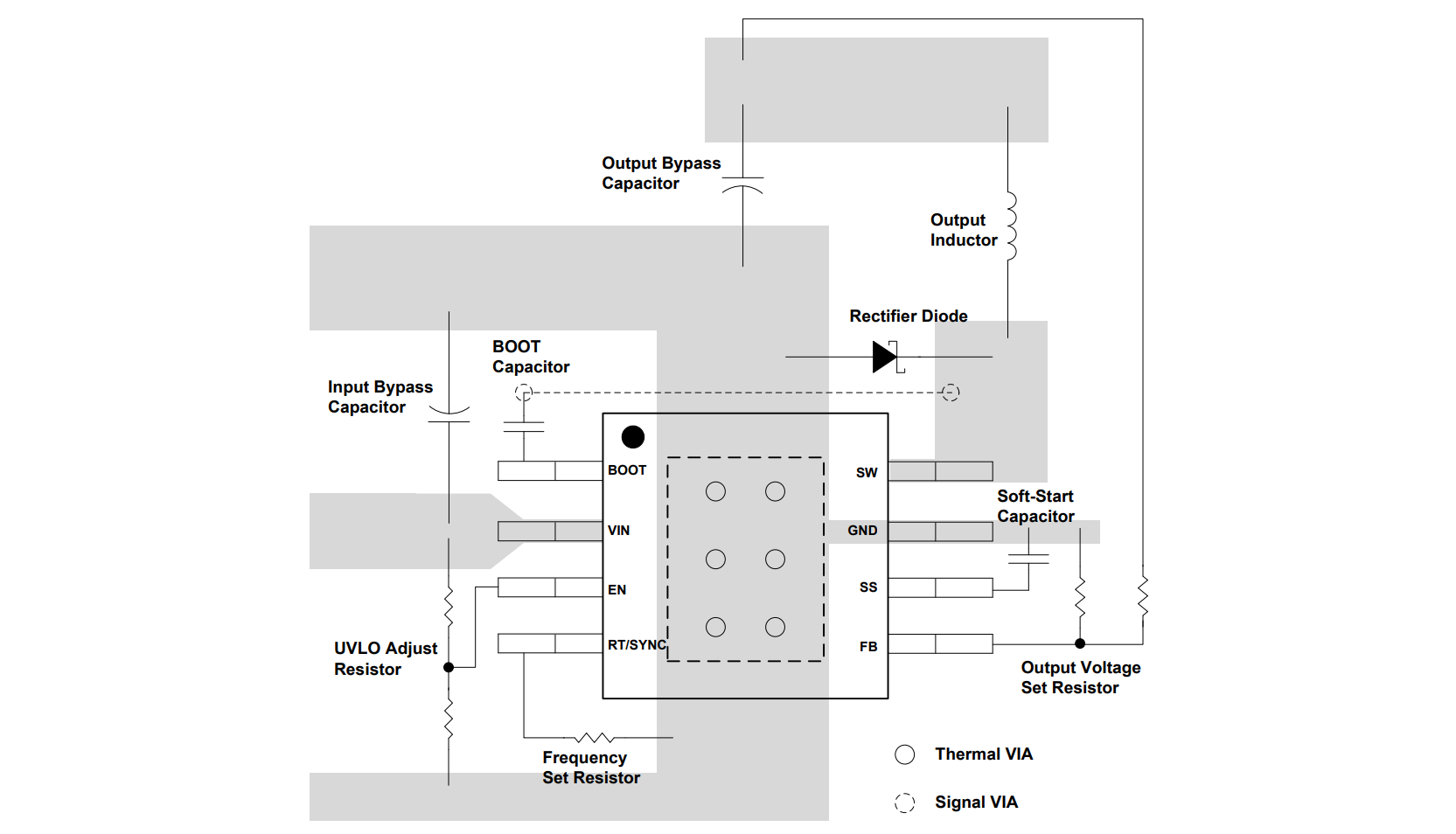

Layout 参考

减小 EMI 的 Layout 建议:

- 反馈网络、电阻 \(R_{FBT}\) 和 \(R_{FBB}\) 应尽量靠近 FB 引脚。 \(V_{OUT}\) 的采样路径应远离噪声产生路径,最好通过屏蔽层另一侧的层。

- 输入去耦电容需要尽可能靠近 \(V_{IN}\) 和 GND 放置。

- 电感应靠近 SW 引脚放置,以减少磁噪声和静电噪声。

- 输出电容 \(C_{OUT}\) 应靠近电感和二极管的节点放置,走线尽可能短,以降低传导和辐射噪声,提高效率。

- 二极管、\(C_{IN}\) 和 \(C_{OUT}\) 的接地连接应尽可能小,并仅在一个点(最好在 \(C_{OUT}\) 接地点)连接到系统接地层,以最大限度地减少系统接地层中的传导噪声。

实际测试

24V 输入,5V/5A 满载输出,实际输出 4.95V/5.00A,纹波 15mV,温度 110℃。

参考与致谢

原文地址:https://wiki-power.com/

本篇文章受 CC BY-NC-SA 4.0 协议保护,转载请注明出处。